雷達系統的數字基帶和射頻域集成挑戰

在本例中,Xilinx應用ChipScope Pro “Core Inserter”通過內部FPGA多路復用器測量核心和FPGA內部路由資源定義探測點。首先,該工具支持用戶定義測量核心類型、信號叢集的數量、用于調試信號的引腳數量以及輸出調試信號的FPGAI/O引腳。

我們可以通過經過上變頻和濾波的I和Q檢測FPGA信號,也可以激勵數模轉換器的數字中頻檢測FPGA信號。然后,稱為“FPGA動態探頭”的邏輯分析儀工具與FPGA測量核心結合,可支持設計人員進行有意義的測量。

邏輯分析儀FPGA探測工具可以大幅簡化測量過程。首先,該工具支持用戶通過JTAG連接直接從邏輯分析儀接口向FPGA下載.bit格式的FPGA設計文件。

其次,該工具可以從Xilinx生成的.cdc文件導入內部探測到的FPGA總線和信號名稱。.cdc文件由Xilinx ChipScope Pro Core Inserter應用軟件創建。之后,稱為“自動引腳映射”的流程將使用邏輯分析儀探測FPGA輸出引腳的調試信號,并自動“映射”至邏輯分析儀的輸入通道。設置邏輯分析儀以獲得適合的已定義時鐘輸入,閥值電平應匹配FPGA輸出電壓電平,邏輯分析儀捕獲模式應匹配FPGA調試信號輸出。設計人員可以選擇要查看的信號叢集。本例選的是數模轉換器輸入。

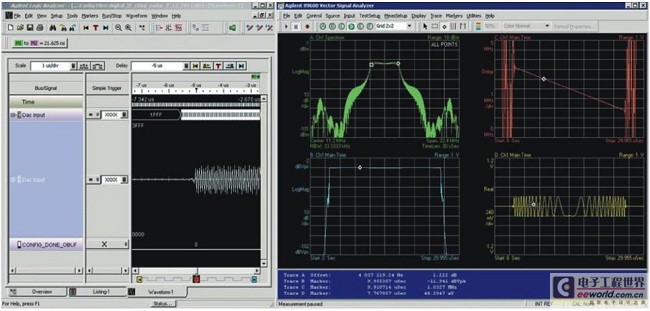

現在,邏輯分析儀捕獲一條數字信號跡線,如圖4左側所示。邏輯分析儀使用了“圖表”顯示模式,其中總線的十六進制值已轉換為波形。我們可以看到數字中頻脈沖的開始。數字基帶團隊和模擬/射頻團隊的通用工具—VSA軟件,能夠導入邏輯分析儀捕獲的數字信號,并以圖4右側所示方式處理數據。但是,我們現在看到的是整個脈沖的線性調頻調制視圖(VSA軟件面板的右上角視圖),還可以看到該數字中頻信號的頻譜分量(面板左上角視圖)。請注意,VSA面板視圖與圖2VSA處理的“黃金標準”仿真基帶信號視圖十分類似。

圖4:應用邏輯分析儀的線性調頻雷達數字中頻信號測量(左)和VSA處理(右)。

借助VSA軟件比較數字中頻和模擬中頻

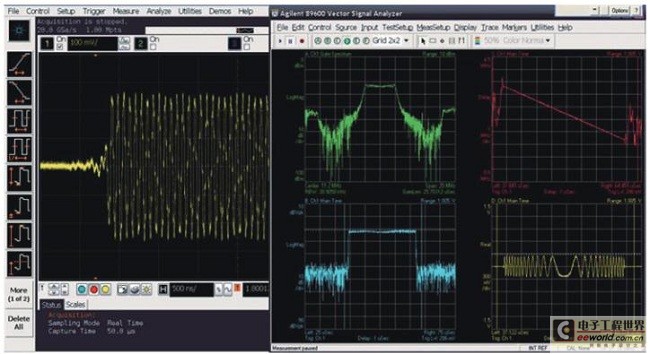

借助VSA軟件可以輕松比較基帶團隊的數字中頻信號以及模擬/射頻團隊的模擬信號。實時示波器可檢測數模轉換器的輸出信號,如圖5左側所示。該信號也可以由VSA軟件導入。VSA軟件可以提供有用的模擬中頻信號信息,如圖5右側的VSA信號處理視圖所示。請注意,本例中系統已正確運行,如圖4右側四個VSA面板視圖顯示的已處理數字中頻信號,我們可以得到一組與圖5右側VSA已處理模擬中頻信號視圖類似的數據。如果路徑中出現多余波形,此類比較分析將十分有用,可以幫助工程師回溯信號路徑中的信號,找出問題的根本原因。

圖5:示波器測得的線性調頻雷達數字中頻信號(左)以及VSA處理結果(右)。

協同調試和驗證

如上所述,我們已了解了通用分析工具VSA在數字和模擬分析流程的應用,以及如何支持基帶和模擬/射頻團隊協作并確定導致設計故障的根本原因。無論FPGA設計人員是否關注數字基帶信號,或者射頻設計人員是否專注系統的模擬和射頻內容,他們都可以借助通用工具來確定導致誤差的原因,或增強對已適合投產的雷達設計的信心。

評論