使用邏輯分析儀快速發現數字系統的問題

邏輯分析儀中的同步和異步捕獲比較

在討論具體的測量實例之前,我們首先來探討一下同步和異步捕獲的差別,以及各自的優點和局限性。

同步(狀態模式)捕獲是指當出現一個相關的有效時鐘信號時,例如在系統時鐘線路上出現上升沿,邏輯分析儀中的測量系統會確定數字并行總線或控制線路的邏輯值。此類測量最主要的目的是確定系統的基本功能是否正常。

相比之下,異步(計時模式)捕獲是指測量系統采用與被測系統“異步”的方式對總線或單獨數字線路的值進行采樣。測量時鐘信號由邏輯分析儀而非目標系統生成。采樣速度一般比目標系統的時鐘速率快,理想情況下,采樣速率是系統時鐘速率的4倍~10倍,這使您可以查看相關信號的“計時”特征。

通過同步捕獲進行功能驗證

當數字設計的物理原型啟動后,許多設計人員首先想要做的便是通過各種同步狀態模式測量,確定系統內部的功能是否正常。如果發現異常,他們將會使用異步計時模式測量來查看是否可以找出問題所在。

假設有一個簡單的8位計數器電路,在這個特殊的實例中,設計將會生成計數器數據,這些數據會在時鐘上升沿之前變得有效和穩定。

通過同步捕獲初步了解計數器電路

通過將邏輯分析儀的8條數據輸入線路連接到電路的8條數據比特輸出線路,可對計數器是否正常工作進行初步的測試。

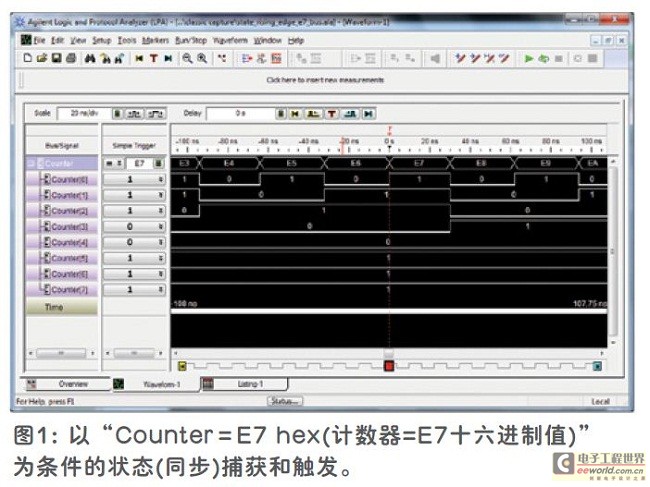

將邏輯分析儀置于“State(狀態)”或同步捕獲模式,并將計時設置為在時鐘信號的上升沿捕獲數據。通過“Waveform(波形)”窗口可以非常輕松地設置簡單的觸發。如圖1所示,可以在總線名稱“Counter(計數器)”旁邊輸入十六進制值E7,定義簡單的觸發事件。

當按下“Run(運行)”后,Waveform視圖中會顯示一個十六進制值序列。如圖1所示,它們看上去進行了適當的計數,要想快速獲得此數據的更完整視圖,可以采用另一種方法“ChartMode(圖表模式)”。圖2為圖表模式視圖,但是看到的不是預期的純凈斜波。

評論