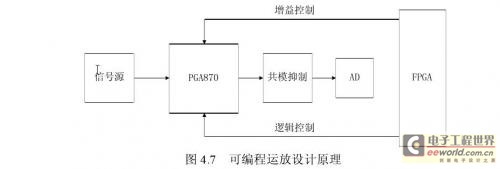

生物電阻抗測量系統中弱信號檢測技術研究--弱信號檢測調理單元設計與實現

PGA870的增益控制實現方式如表4.4所示,表中未列出全部控制組合,其增益按B0至B5變化組合以0.5dB步進。

4.2.4 ADC前端共模抑制模塊

4.2.4.1 ADC前端電路

生物電阻抗測量系統中,信號采集的是直流信號,對于這種信號,不能用阻容耦合或變壓器耦合的方式,宜采用直接耦合放大電路但存在零點漂移。所謂零點漂移是指當輸人信號為零時,在放大器的輸出端出現一個變化不定的輸出信號的現象,簡稱零漂。前級的漂移被后級放大,因此嚴重干擾正常信號,級數越多,漂移越嚴重,甚至使放大器不能正常工作。在電路結構上,采用差分電路是目前應用最廣泛的能有效抑制零漂的方法。

差分放大電路又叫差分電路,它能有效的減小由于電源波動和晶體管引起的零點漂移,因而獲得廣泛的應用。

差分電路的輸入端有兩個信號的輸入,這兩個信號的差值,為電路有效輸入信號,電路的輸出是對這兩個輸入信號之差的放大。設想這樣一種情景,如果存在干擾信號,會對兩個輸入信號產生相同的干擾,通過二者之差,干擾信號的有效輸入為零,這就達到了抗共模干擾的目的。

差分放大電路的特點:

1.由兩個完全對稱的共射電路組合而成。

2.電路采用正負雙電源供電。

3.極強的共模抑制能力。

4.2.4.2共模抑制比

為了說明差分放大電路抑制共模信號的能力,常用共模抑制比作為一項技術指標來衡量,其定義為放大器對差模信號的電壓放大倍數Aud與對共模信號的電壓放大倍數Auc之比,稱為共模抑制比,英文全稱是Common Mode Rejection Ratio,因此一般用簡寫CMRR來表示。

差模信號電壓放大倍數Aud越大,共模信號電壓放大倍數Auc越小,則CMRR越大。此時差分放大電路抑制共模信號的能力越強,放大器的性能越好。當差分放大電路完全對稱時,共模信號電壓放大倍數Auc=0,則共模抑制比CCMR→∞,這是理想情況,實際上電路完全對稱是不存在的,共模抑制比也不可能趨于無窮大。

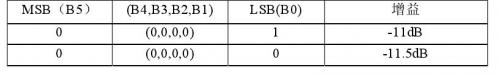

本文采用電路完全對稱的差分電路以做到阻抗匹配和ADC前端調理,如圖4.8所示:

圖中芯片仍為PGA870可變增益放大器,其輸出方式為全差分的,能有效的抑制環境中的共模干擾,其CMRR可達到76db,PGA870的輸出端采用RC網絡進行信號的端接,能有效的減小信號的反射,并采用交流耦合的方式將信號傳送至后端ADC芯片。圖中信號線ADC_VCM提供差分信號合適的直流偏置,在信號線ADC_IN2+和ADC_IN2-上串接5歐姆的電阻來減小反射過沖電流的大小。

4.3時鐘模塊設計

4.3.1時鐘電路設計分析

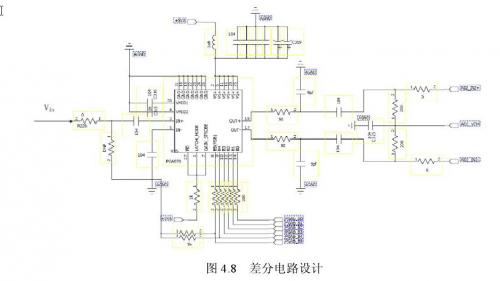

時鐘對于高速ADC系統而言尤其關鍵,這是因為時鐘信號的時序準確性可以直接影響ADC的動態特性。理想的時鐘源是不會抖動的,因此ADC可以精確的在每個固定的時間間隔進行采集,但是實際電路中各種不確定的因素都會造成時鐘的抖動。如圖4.9所示,這種時序的不確定性帶來的結果是采樣波形出現一個為eΔV的誤差電壓,這相當于在原信號上引入了新的噪聲,從而ADC的信噪比會受到數據轉換過程的影響。

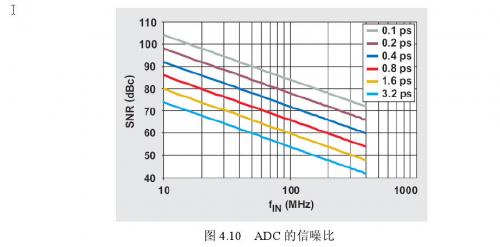

這種噪聲反映在ADC的信噪比上就形成了如圖4.10所示曲線,隨著采樣頻率的提高,時鐘抖動對于系統信噪比的影響越來越大,而同一頻率時,高的時鐘抖動也比低的時鐘抖動給系統帶來更多的誤差。

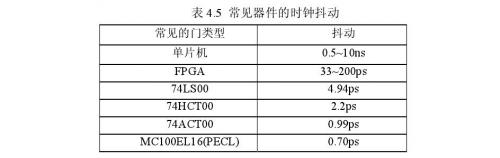

下表4.5是常用的一些器件,在很多設計中傾向于直接由數字器件(FPGA,MCU,DSP)產生一個時鐘來作為ADC的采樣時鐘,這也是為什么ADC精度總是達不到手冊上描述的指標的原因,時鐘因素制約了系統性能的提高。

典型的高速ADC使用兩個時鐘脈沖邊沿引起各種各樣的內部時間信號,并且可能影響到敏感的時鐘占空比。通常,為了維護動態性能特征需要容忍5%時間占空比。

AD9216為每個通道提供分開的時鐘輸入。最好的方案是兩個通道的時鐘工作在相同的頻率和相位上。兩個通道的時鐘異步時可能使每個通道轉換性能有所下降。在某些應用中,相鄰兩通道之間存在時鐘偏差是可以允許的,AD9216當分開的時鐘存在輸入偏差時(典型值±1ns)不會有重大性能退化,本系統中的AD9216的每個通道都選擇相同頻率和相位的時鐘。

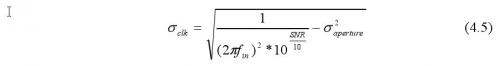

根據抖動和ADC信噪比的關系:

其中,Tσ表示總抖動,clkσ表示采樣時鐘的抖動,apertureσ表示ADC的孔徑抖動,in f代表輸入信號頻率。

采樣時鐘的抖動和信噪比的關系可有下述公式導出:

所以一個高質量的時鐘源是保證ADC系統精確的關鍵。在器件的選擇上尤其要關注芯片引入的抖動,因此要得到較高的信噪比就要選用抖動較小的時鐘源。下面介紹幾種常用的ADC時鐘設計方案:

評論