基于用CPLD實現FIR數字濾波器的設計

Altera公司的FLEX10K是工業界第一個嵌入式的PLD,具有高密度、低成本、低功率等優點。器件的主要結構特點是除主要的邏輯陣列塊(LAB)之外,首次采用了嵌入陣列塊(EAB)。每個陣列塊包含8個邏輯單元(LE)和一個局部互連。一個LE又由四輸入查找表(LUT)、一個可編程寄存器和專用的載運和級聯功能的信號通道所組成。

在FLEX10K器件中,把每一組邏輯單元(8個LE)組成一個邏輯陣列塊(LAB),所有的邏輯陣列塊(LAB)排成行和列。在一行里還包含一個單一的EAB。多個LAB和多個EAB采用快速通道互相連接。

嵌入式陣列塊(EAB)是FLEX10K系列器件在結構設計上的一個重要部件。它是一個輸入端口和輸出端口都帶有寄存器的一種靈活的RAM塊,嵌入陣列塊(EAB)組成的規模和靈活性對比較多的內存是適宜的。功能包括乘法器、向量的標準和誤差矯正電路等。在應用中,這些功能又能夠聯合完成數字濾波器和微控制器的功能。

采用可編程的帶有只讀平臺的嵌入陣列塊(EAB)在配置期間可執行邏輯功能并建立一個大的查找表(LUT),在這個查找表里用查找的結果執行組合邏輯函數,而不用計算它們。顯然,用這種組合邏輯函數執行比通常在邏輯里應用算法執行要快,而且專用EAB容易應用,并且快速提供可能預測的延遲。

本文介紹了應用Altera 公司的FLEX10K系列CPLD快速完成卷積的方法實現有限沖激響應(FIR)濾波器的設計。

查表法實現卷積運算方法

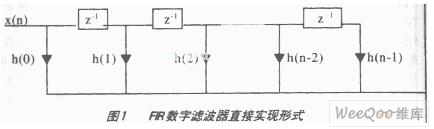

有限沖激響應(FIR)濾波器的基本結構如是一個分節的延時線,把每一節的輸出加權累加,得到濾波器的輸出。數學上表示為:

結構如圖1所示。它由用一條均勻間隔抽頭的延遲線上對抽頭信號進行加權求和構成。

根據上式,可以看出FIR數字濾波器涉及到大量的卷積運算,使用常規硬件實現時會占用大量的資源。通過充分利用FLEX10K系列芯片所具有的查表結構,將卷積運算轉化為查表移位求和來實現。例如:對于式

y = [ x(1) h(1) ]+[ x(2) h(2) ]+[ x(3) h(3) ] + [ x(4) h(4) ] (1)

假設x和h 都是無符號整型二進制數,寬度兩位,取值兩位如下:

h(1)= 01,h(2)= 11 ,h (3)= 10, h(4)= 11

x(1)= 11,x(2)= 00, x (3)= 10, x(4)= 01

從圖2可以看到式(1)運算的實現。中間數據p1(n)中的4個數據實際上是乘數x(n)的最低位比特與h(n)相乘的結果,并且該值不是0就是h(n)。進一步考慮,中間數據p1和p2的值,既“100”t3.gif (8144 字節)和“011” 是由不同的h(n)之和構成,而對h(n)的選擇是由乘數x(n)的相同位的比特決定的。例如上圖x(n)的最低位為1001,則p1的值為h(1) + h(4);其高位為1010,則p1的值為 h (1) + h(3)。因此利用Altera公司FLEX器件中的查找表(LUT)結構,預先將h(n)的各種組合存入查找表,則上例中的原需4次乘法和3次加法的卷積運算轉化為1次加法。圖3顯示了用查找表實現該例的結構。

評論