一種2Gsps數字示波器數據采集系統的設計

3.2 AT84AD001工作模式的設置

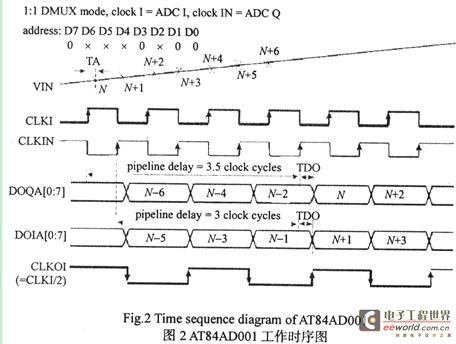

AT84AD001的工作時序如圖2所示。I,Q通道ADC都使用I通道輸入模擬信號,I通道工作時鐘頻率為1 GHz,Q通道的工作時鐘與I通道工作時鐘同頻反相,在這種模式下,通過兩個實時采樣率為1 Gsps的ADC按照交替方式并行采樣,將得到的數據按照一定的輸出格式拼合成2 Gsps的數據流。

3.3 FPGA內部邏輯模塊介紹

FPGA內部邏輯模塊主要包括:

1)時基電路模塊:接收AT84AD001的輸出數據同步鎖存時鐘作為FPGA內部的工作時鐘,并且為數據采集系統提供時間基準尺度。

2)數據采集接口、存儲接口模塊:利用

FPGA的串行收發器SERDES(Serializer/Deserializer)和動態相位對準DPA(Dynamic Phase Alignment)電路接收LVDS格式、1 Gbps速率的差分數據流,并且對其降頻,然后根據差分通道和ADC數據位的對應順序以及接收器數據的輸出格式,設計恢復電路,將64位的數據按采樣點的格式恢復為8個采樣點,最后在FPGA與片外存儲器之間建立數據存儲接口,將數據按照一定的速率和格式寫入片外存儲器。

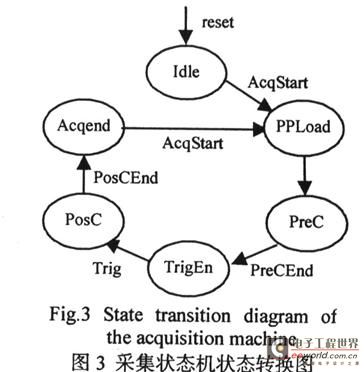

3)采集控制模塊:利用采集狀態機,配合軟件系統完成對整個采集過程進行管理,按照設定的預觸發和后觸發數據量完成成整個采集工程。

4)觸發控制模塊:用來實現信號特征點的捕捉及波形顯示的同步。

5)計算系統接口模塊:完成FPGA和DSP之間的通信。

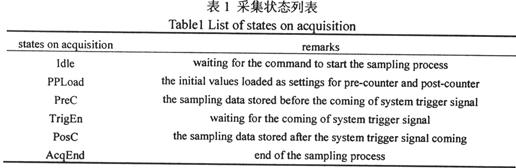

其中,采集狀態機作為采集控制模塊的核心,負責整個數據采集過程的控制,具有舉足輕重的地位。它是一個用VHDL語言編制的狀態機,其狀態轉換如圖3所示。圖3中狀態轉換所涉及的采集狀態說明如表1所示。

4 數據采集系統監控軟件設計

為了便于測試整個硬件的工作,在DSP中編制了簡單的監控程序,程序流程圖如圖4所示。首先,DSP調用時鐘芯片和ADC的初始化程序,完成對高速時鐘電路和采集電路的初始化,使其工作在目標系統所需要的工作模式下;然后發出采集開始命令,數據采集系統進入采集過程;延遲一段時間以后,查詢采集結束標志;當得知采集過程結束時,便從RAM中讀取波形數據,經過分析處理后送去顯示。

評論