可能會對高速數據傳輸造成損害的因素以及測試過程分析

多年來,寬同步并行總線已成為數字設備之間進行數據交換的主要技術手段。通過并行移動多個比特,這些數據總線技術好像比串行(順序)傳輸技術的通信速度更快。但遺憾的是,并行總線定時同步(時滯)在時鐘頻率和數據傳輸率較高時存在嚴重的問題,這明顯限制了并行總線傳輸的速度。

此外,這一技術在支持長距離、實施成本和最終用戶成本方面也面臨重大挑戰。通過比較,串行總線只發送一個比特流并具有“自時鐘”機制,因此數據和時鐘之間沒有時序偏差(即同時傳輸的比特到達時間之差)。借助串行傳輸,消除了信號同步問題,而且整體性能更強。然而,隨著技術進步,這個性能障礙得到解決,另一個問題又出現在人們面前。速度更快的新技術在化解此項挑戰的同時,也使設計更趨復雜,而且持續變化的標準也產生了更多新的設計難題,這會妨礙產品快速上市并增加開發成本。包括 PCI-Express、XAUI、RapidIO、USB, HDMI 和 SATA 在內的一些新的串行數據總線架構所帶來的數據處理量比幾年前要大好幾個數量級。

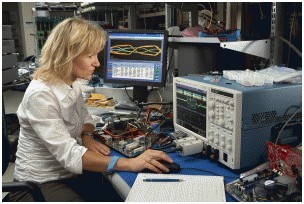

為了確保產品開發的所有階段之間的交互操作性,標準化勢在必行。領先的技術公司已經將2.5-Gbit/s 和 3-Gbit/s的設計產品化,而5-Gbit/s 技術也即將面世,同時,10Gbs 已經用于網絡通信的設計。在如此復雜多變的環境下,工程師極需一些測試解決方案,幫助其迅速輕松地發現和糾正設計中的問題。在此,泰克提供了完備的串行數據測試解決方案,有助于工程師開發產品,并能夠確保符合最新的串行數據測試要求。

測試高速串行數據總線

在設計過程中,工程師需要確認高速串行總線能夠正確傳送數據,同時串行傳輸問題也不會給其他系統元件帶來不利影響。最新標準具有更快的邊緣速率和更窄的數據脈沖,對驗證、調試和測試過程提出了一些獨特且嚴格的要求。

隨著數千兆數據傳輸率在數字系統中屢見不鮮,信號完整性(即集成電路正確運行所具備的信號質量)也逐漸成為設計人員關注的重點。數據流中一個比特的錯誤都會對指令或數據交換處理的結果產生巨大的影響。

可能會對傳輸信號質量造成損害的因素包括:

千兆信號速度:超高速傳輸率、低電壓差分信號和多級信號傳輸更容易引起信號完整性問題、差分時滯、噪音和模擬干擾的問題。由于串行總線可以為單通道架構,也可以為多通道架構以提升數據量,此時將造成整體設計更復雜并可能引起通道時滯定時干擾問題。

抖動:由于較高的數據速率和嵌入的時鐘的影響,現代串行設備會很容易受到抖動的影響,抖動會產生傳輸錯誤并導致比特差錯率,性能下降。抖動通常使信號偏離理想的時間。抖動通常源自串擾、系統噪音、同步開關輸出和一些其他的常見干擾信號。

傳輸線影響:傳輸線作為電源和信號傳輸的中介,可以是簡單的無源線路元件,如電線、電纜和芯片印刷電路板(PCB)互連。借助串行數據技術,信號發送器、傳輸線和接收器共同構成了串行數據網絡。而由此帶來的傳輸效應(如反射和阻抗不連續)會嚴重影響信號質量并導致傳輸錯誤。

噪音:噪音是在采樣數據中出現的任何多余的信號。噪音來自外源(如 AC 電源線)和內源(如數字時鐘、微處理器和開關電源)。噪音可能是瞬時的,或者是寬帶隨機噪音,但都會引起抖動和信號完整性問題。

帶有嵌入式時鐘的高速數字信號具有越來越像模擬系統的特征,使設計驗證和系統集成面臨更嚴峻的挑戰。由于信號即使在很小的失真或抖動下都可能使系統變得不穩定,這令用戶在各種條件下實施精確驗證、特征描述和強度測試都要面臨新的問題。

高速串行數據測試過程

受消費需求的推動,設計工程師經常需要將新功能集成到采用領先技術的系統設計中。為了便于工程師使用,每種串行數據技術的設計和操作都會在唯一的標準文檔中進行定義,該文檔通常由行業委員會編寫。每個標準還必需經過專業測量和一致性測試過程,這就給現有復雜的設計任務又增加了新的工作。這些標準針對高速數據信號傳輸和編碼、封裝、時鐘嵌入、傳輸屬性和一致性測試過程。設計人員根據明確的高速串行技術標準和測試程序,方能夠創造出具有良好互操作性的產品。

典型的高速串行數據測試過程包括:

- 設計驗證:設計和測試工程師需要驗證其設計在實際的操作中是否符合設計仿真、技術指標以及具有全部功能。這需要在現實和極限強度條件下進行全面的特征描述、調試和分析。

- 特征描述:在元件的初始測試中,設計人員將描述性能特征,從而確定信號行為是否符合規范。通常需要進行大量地精確測量,從而確定高速總線是否工作正常。特征描述通常包括測量上升/下降時間、邊緣到邊緣時間、抖動和抖動容限、信號路徑的時滯、總線建立時間和數據路徑變化。

- 排除故障:對于任何被發現的特征描述或操作問題,工程師都需要進行調試并查出故障或異常條件,如硬件時間、串擾、信號質量和/或軟件設計問題等。

- 一致性測試:為確保多個供應商和產品之間能夠即插即用,相互兼容,設計師必需確認最終設計符合行業特定的串行數據標準。一致性測試是一個復雜且比較耗費時間的環節,而且通常需要高級測試和分析功能。在串行標準的一致性測試規范中,通常包括幅度、定時、抖動、阻抗和眼圖測量。

通常工程師需要全面評估芯片和系統性能。在千兆赫速度下,抖動、發射器和接收器之間的阻抗不連續,或者硬件和軟件之間的系統級干擾都會引起定時問題。每個設計階段都需要全方位的分析工具進行更深入的觀察,進而全面描述特征并發現隔離邊緣設計或系統影響。

領先的設計、縮短產品開發周期、擴展供應鏈和符合特定技術標準都必需要通過優秀的驗證和測試工具實現。借助先進的數據分析能力,泰克的測試和測量儀器是用戶在開發過程早期發現設計問題,縮短串行數據產品的設計周期,加快進入市場的時間以及降低成本的有效手段。敬請關注下一篇博文:主要的高速串行接口技術及測試解決方案

評論