信號完整性分析基礎系列之三--串行數據測試中的CDR

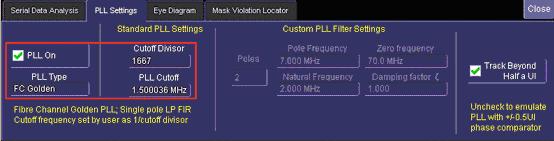

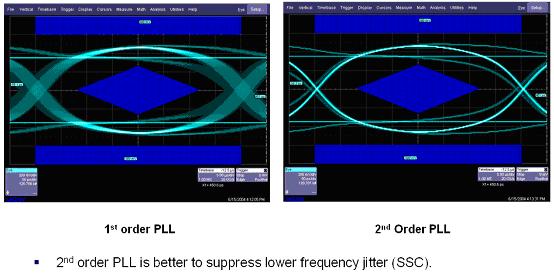

如下圖4所示為力科串行數據分析儀中PLL設置的參考,缺省情況下使用FC Golden PLL,該PLL為1階鎖相環,其環路帶寬等于比特率除以1667,最早是在Fibre Channel的MJSQ文檔中定義的。

圖4:力科串行數據分析儀的軟件CDR設置界面

如下圖5為使用力科示波器測量某2.5Gbps信號,當示波器的串行數據分析軟件的PLL帶寬在2MHz、5MHz、10MHz、20MHz四種設置下的眼圖測量結果,可見,PLL帶寬越高,眼圖越清晰,抖動越小。問題是,待測試電路的收發器RX端接收到的、真實的眼圖和抖動是什么樣呢?答案是必須把示波器的CDR參數設置得和待測試電路RX端的CDR參數完全一致,這樣示波器的測量結果才具備參考價值。

圖5:示波器在不同PLL設置時測量同一信號的眼圖

在圖4和圖5中都是一階鎖相環的CDR,在很多的串行電路標準中都使用這類PLL,比如GBE、XAUI、SDH、CPRI、FC、SAS等等。不過,PCIe Gen2、SATA2、Displayport則使用了二階鎖相環的CDR,如圖6所示為一階PLL和二階PLL的JTF對比,二階PLL有更加陡峭的滾降系數-40dB/decade(一階PLL的滾降系數為20dB/decade)。假設某500kHz的抖動為150ps(而且500kHz在斜線的頻段內),通過一階PLL后抖動只有15ps,而通過二階PLL后僅為1.5ps。可見,對于圖6中低頻段的抖動,二階PLL可以更大幅度的降低該頻段的抖動。

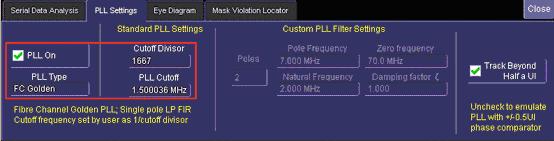

圖7所示為某2.5Gbps信號,CDR使用一階PLL或二階PLL的眼圖測量結果,可見,使用二階PLL得到的眼圖非常清晰、抖動更小。二階PLL可以更大程度的減小低頻抖動,通常用于帶有擴頻時鐘(SSC)的串行數據信號,比如計算機主板上的SATA和PCIe。

圖7:示波器在不同PLL設置時測量同一信號的眼圖

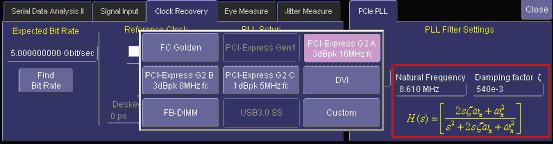

如下圖8所示,在力科SDA中,集成了FC Golden, PCIe Gen1, PCIe Gen2, DVI, FBDIMM, USB3.0和Custom多種PLL參數設置,測量時根據待測試信號的類型選擇合適的CDR設置。

圖8:力科示波器集成了多種PLL設置

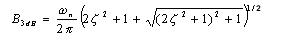

在Custom自定義鎖相環模式下,可以選擇1階PLL還是2階PLL。如果是自定義的1階PLL需要設置極點和零點的頻率,PLL的截至頻率就是極點頻率,零點頻率必須高于前者,其決定了阻帶的衰減系數;如果是自定義2階PLL需要設置Natural Frequency(ωn)和Dampling factor(ζ),如圖8紅色標記所示,該PLL的環路響應的傳遞函數為H(s)(圖8中黃色字體的公式),截至頻率可用下面的公式計算:

綜上所述,正確設置示波器的CDR參數是測量眼圖和抖動的關鍵,測試人員需要參考串行數據規范或儀器廠商的操作文檔,才能保證測量的準確性和有效性。

參考文獻

1, Fibre Channel – Method Jitter and Signal Quality Specification – MJSQ, T11.2/Project 1315-DT/Rev 14.1, June 5, 2005.

2, Mike Peng Li, "Jitter, Noise, and Signal Integrity at High-speed".

評論