數字示波器之DMA高速數據采集方案設計

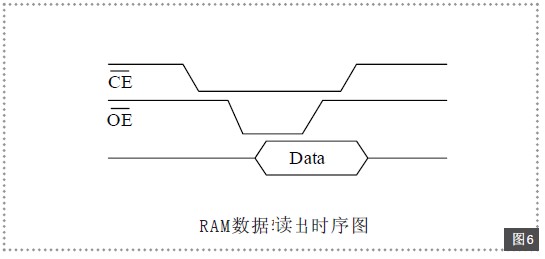

數據寫入RAM后,還要能夠被MCU從RAM中獲取,RAM數據讀出時序如圖6所示。

從圖中看出,當CE=0;OE=0時,RAM將地址選擇的內部單元數據輸出到數據總線從而可以被MCU讀取。

這里有一個問題要考慮清楚,為了實現ADC結果直接存入RAM,已經將5510的數據線和RAM的數據線直接相連了,現在還要將MCU的數據線和RAM的數據線相連,會不會出現數據沖突?其實只要器件數據線具有三態功能,就能夠實現數據線分時復用,通過控制電路實現數據總線上某階段只能有一個數據輸出源,例如當ADC直接給RAM存入數據時,MCU要讓出數據總線,當MCU讀取RAM數據時,ADC要高阻態隔離數據總線。

三、控制電路設計

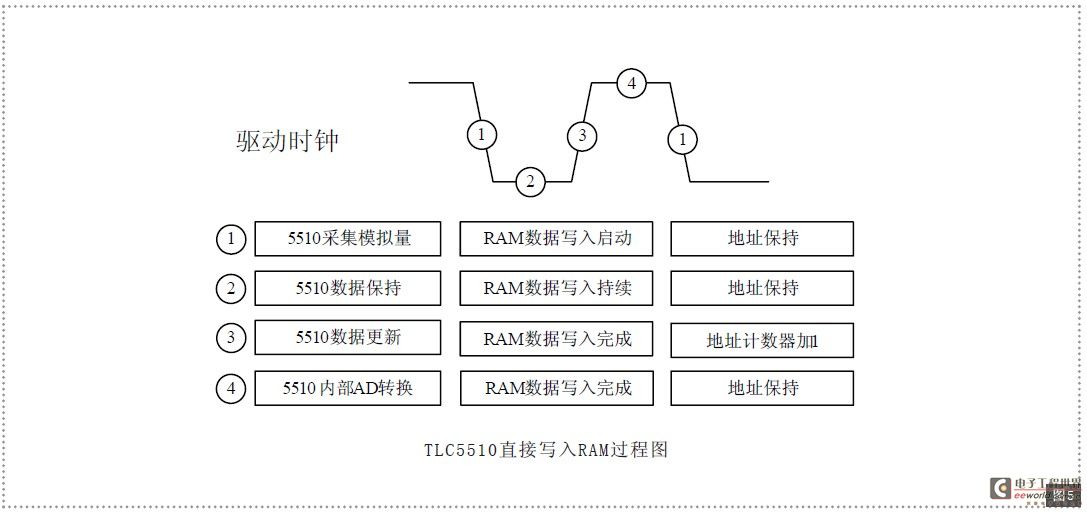

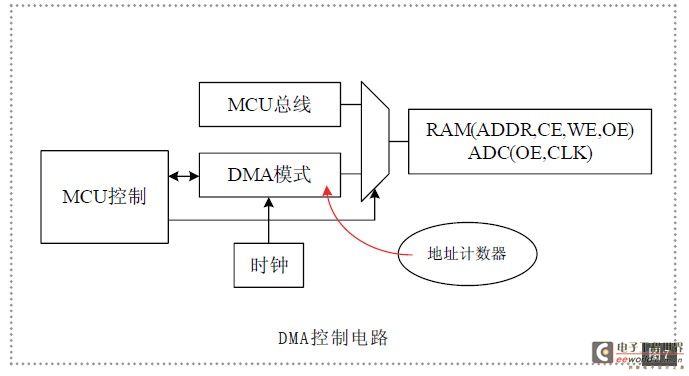

控制電路原理如圖7所示,在MCU的控制下,RAM和ADC的控制信號通過多路選擇器選擇與MCU總線模式或DMA模式相連,這兩種模式被MCU完全控制,可以自由切換,當選擇DMA模式時,MCU首先要讓出數據總線,確保ADC與RAM占用數據總線,此時,RAM的地址由地址計數器產生,RAM_CE=0(片選有效);RAM_OE=1(禁止讀);ADC_OE=0(內部數據總線上的數據直接輸出到外部數據總線上);RAM_WE與ADC_CLK、地址計數器共用同一時鐘信號,按圖5中4節拍實現AD轉換后數據直接存儲到RAM中,DMA過程在MCU清零地址計數器后開始,沒一個時鐘周期AD輸出一個數據直接存入RAM,同時地址計數器加1,當地址計數器溢出后被MCU檢測到則表示一幀數據采集完成。

一幀數據采集完成后,MCU切換到MCU總線模式讀取RAM的結果,這時RAM_CE=0(或接MCU地址引腳);RAM_OE=RD(MCU讀控制信號);ADC_OE=1(禁止ADC數據占用數據線);RAM_WE=WR,ADC_CLK=0,這時MCU可以自由讀取RAM。

圖7所示邏輯電路用硬件描述語言在CPLD上實現非常方便,請讀者吸收DMA設計思路后自己完成電路設計。

四、結束語

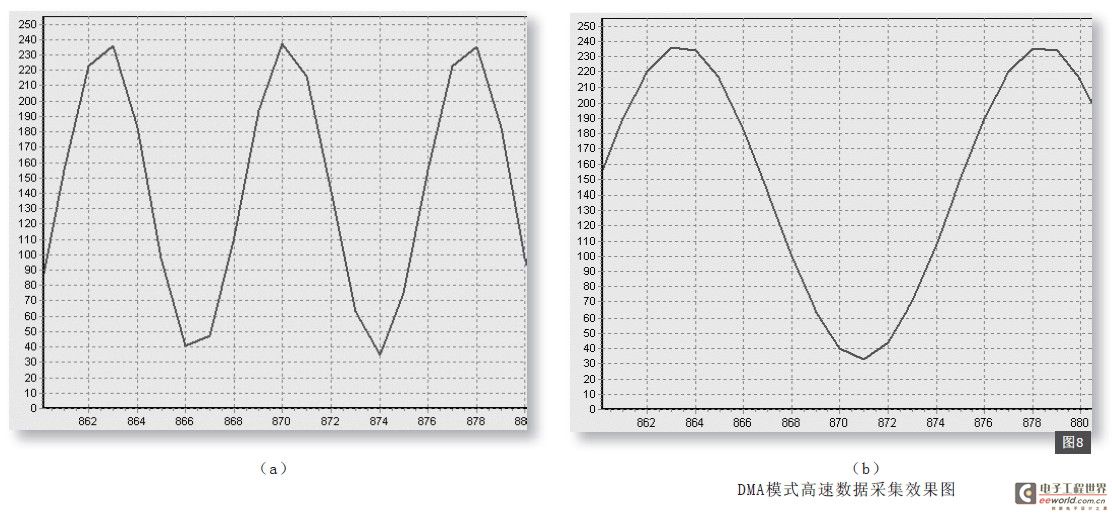

筆者完成的DMA高速數據采集卡對2MHz、1MHz的正弦信號采樣并繪圖效果如圖8(a)、(b)所示。對于低于1MHz的正弦信號采集后能夠非常光滑清晰的還原出正弦波形。在CPLD內部時鐘精確分頻后還可以實現多頻點采樣,例如20MHz采樣,10MHz采樣,1MHz采樣。

評論