CRC校驗的LabVIEW實現(xiàn)

內容:

循環(huán)冗余校驗碼(CRC)的手算過程:

原始報文為1010

生成多項式G(X)=X3+X+1: 生成多項式G(X)=X3+X+1轉換成對應的二進制除數(shù)為1011。

用生成多項式對應的二進制數(shù)對左移3位后的原始報文進行模2除(高位對齊),相當于按位異或:

1010000

1011

------------------

0001000

0001011

------------------

0000011

得到的余位011,所以最終編碼為:1010 011

編寫程序模擬計算CRC的過程,可以得到CRC校驗的結果。

同時還有另一種模擬CRC電路工作方式的CRC實現(xiàn)方法:

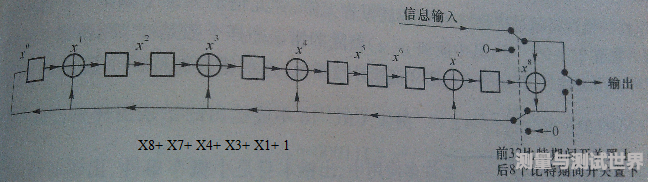

其電路的原理圖如下:(32bit數(shù)據(jù)+8bit CRC,生成多項式為:X8+ X7+ X4+ X3+ X1+ 1)

這種方式下,從第一個比特數(shù)據(jù)直接開始異或計算,最后一個數(shù)據(jù)輸入后,寄存器中的各個數(shù)據(jù)即為CRC校驗位

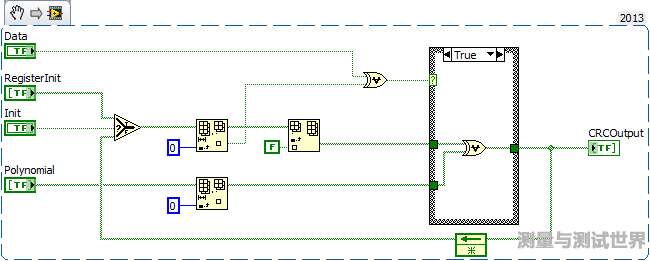

LabVIEW下的CRC計算可以模擬上述電路圖的工作過程。

- 對各寄存器中的數(shù)據(jù)向高位移位,并取得最高位數(shù)據(jù),最低為在移位中補0。

- 1中取得的最高位數(shù)據(jù)與輸入數(shù)據(jù)異或,異或的結果決定后續(xù)是否進行3操作。

- 如果2中異或結果為真,使用多項式對寄存器中數(shù)據(jù)異或。

具體LabVIEW代碼見下圖:

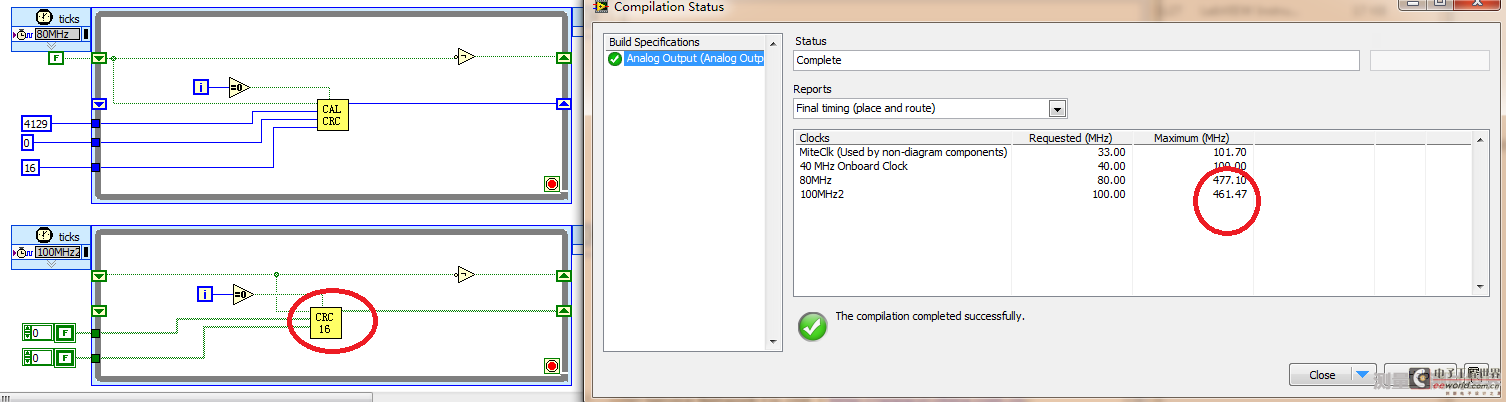

該CRC代碼的主要特性有:

1.支持FPGA端的定時循環(huán)(FPGA定時循環(huán)內,CRC16的速率約460M)

2.支持實現(xiàn)任意位、任意生成多項式、任意寄存器初始值。

3.直接從第一個數(shù)據(jù)開始計算CRC,并在最末數(shù)據(jù)輸入后,直接得到CRC結果,使用方便。

4.支持CRC計算與校驗

評論