再談示波器帶寬

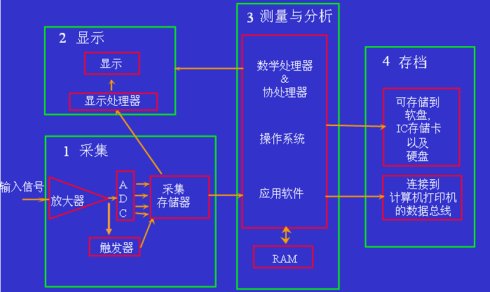

圖1,數(shù)字示波器的原理框圖

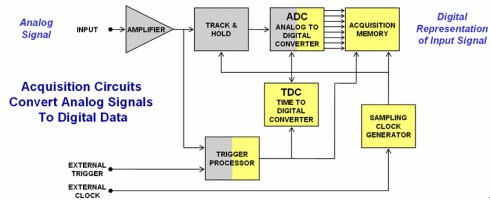

捕獲部分主要是由三顆芯片和一個(gè)電路組成,即放大器芯片,A/D芯片,內(nèi)存芯片和觸發(fā)器電路,原理框圖如下圖2所示。被測信號首先經(jīng)過探頭和放大器及歸一化后轉(zhuǎn)換成ADC可以接收的電壓范圍,采樣和保持電路按固定采樣率將信號分割成一個(gè)個(gè)獨(dú)立的采樣電平,ADC將這些電平轉(zhuǎn)化成數(shù)字的采樣點(diǎn),這些數(shù)字采樣點(diǎn)保存在采集內(nèi)存里送顯示和測量分析處理。

圖2,示波器捕獲電路原理框圖

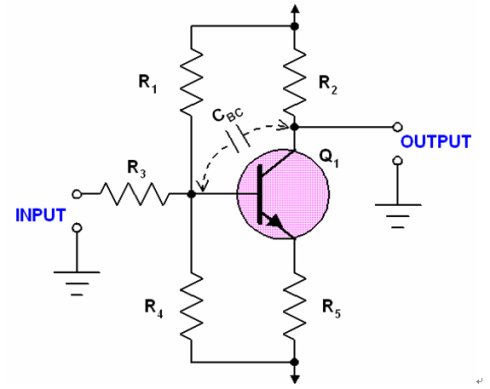

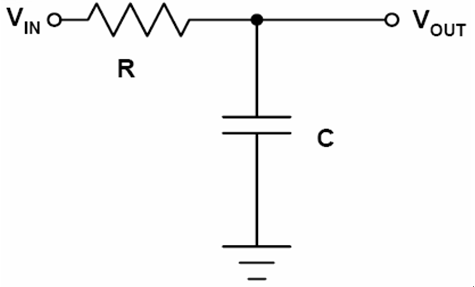

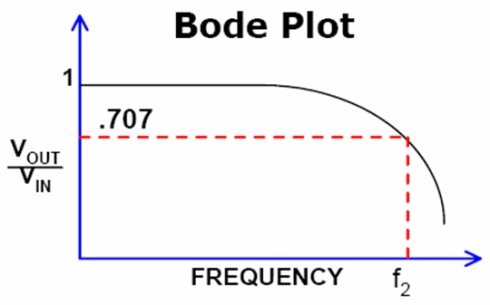

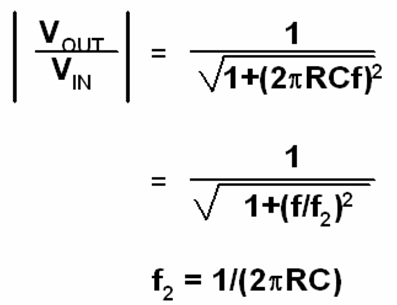

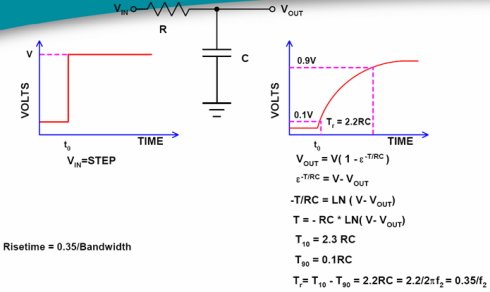

至此,我們知道帶寬f2即輸出電壓降低到輸入電壓70.7%時(shí)的頻率點(diǎn)。 根據(jù)放大器的等效模型,我們可進(jìn)一步推導(dǎo)示波器的上升時(shí)間和帶寬的關(guān)系式,即我們常提到的0.35的關(guān)系:上升時(shí)間=0.35/帶寬,推導(dǎo)過程如下圖6所示。 需要說明的是,0.35是基于高斯響應(yīng)的理論值,實(shí)際測量系統(tǒng)中這個(gè)數(shù)值往往介于0.35-0.45之間。在示波器的datasheet上都會(huì)標(biāo)明“上升時(shí)間”指標(biāo)。 示波器測量出來的上升時(shí)間與真實(shí)的上升時(shí)間之間存在下面的關(guān)系式。在對快沿信號測試中,需要通過該關(guān)系式來修正實(shí)際被測信號的上升時(shí)間。

Measured risetime(tr)2 = (tr signal)2+(tr scope)2+(tr probe)2

圖6,示波器上升時(shí)間和帶寬的關(guān)系

示波器前端放大器幅頻特性的波特圖是新示波器發(fā)布的“出生證”。

評論