信號完整性系列之十八——帶有預加重和均衡的高速信號測

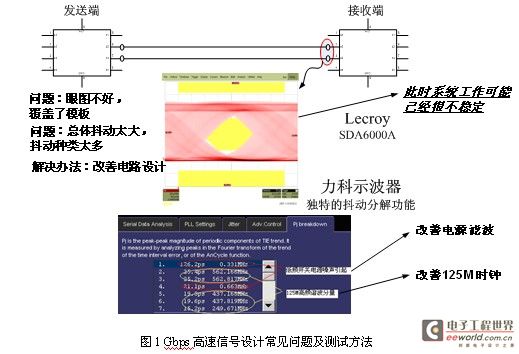

在速率達到Gbps高速設計中,最常見的問題通常會是眼圖不好、抖動過大等等。如圖1所示,接收端芯片管腳處眼圖很差,抖動成分很復雜。對于這樣的問 題,如果我們使用力科示波器配有的獨特的抖動分解功能對抖動進行分解分析可以清楚的看到主要的抖動來自于330khz頻點和125MHZ的諧波(如 250MHZ、560MHZ左右)的頻點,根據這些頻點,我們可以更快捷更容易的發現此系統的問題主要可能是因為電源部分和125MZH時鐘電路設計得不 夠完善,這樣我們就可以有針對性的去改善這些電路。

本文引用地址:http://www.104case.com/article/201701/336519.htm

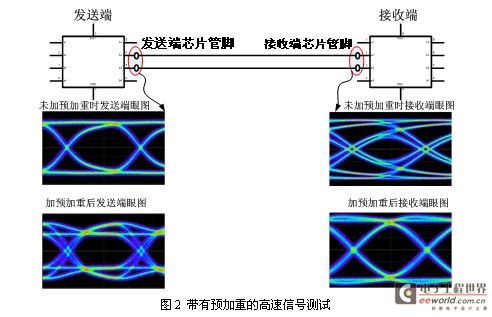

當信號速率進一步提升后,僅改善設計電路可能并不能夠完全改善信號眼圖,此時發送端芯片一般會具備預加重調節功能,但是需要設計工程師去調節預加重為最優 值以確保接收端信號眼圖最優化。如圖2所示,未加預加重/去加重時候,發送端眼圖很好,但是接收端眼圖很差;增加預加重后,接收端眼圖得到有效的改善。由 于芯片廠商一般會提供多種預加重的程度和幅度的調節,所以工程師們通常需要設法選擇最優的,一般方法都是通過測試接收端的信號,每調節一次預加重,測試一 次接收端信號眼圖,需要經過很多次測試對比才能找到最優值,通常效率會比較低。

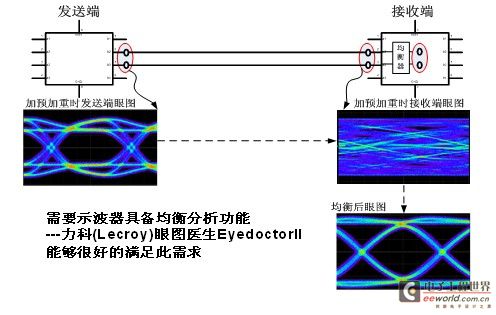

當信號速率更高時,通常達到5Gbps以上時,僅靠調試電路、調節發送端芯片預加重都難以改善接收端信號的眼圖,如圖3所示,發送端確實已經增加了預加 重,但是接收端眼圖仍舊閉合了,對于閉合的眼圖就無法對其進行分析,而奇怪的是即使眼圖如此糟糕,但是系統卻仍舊工作良好,那么這是為什么呢——因為芯片 接收端采用了均衡技術,雖然在接收端管腳處測得的眼圖已經趨于閉合,但是均衡后的眼圖通常會得到很好的改善。如圖3右側下方均衡后的眼圖已經很好了,但是 從圖中可看出均衡后的點是在芯片內部,示波器可能不能夠直接測試到均衡后的信號,而我們真正需要分析的其實是均衡后的眼圖。那么大家應該會問,這樣的話示 波器在接收端已經測不到均衡后的信號,那么示波器還有什么用呢,在接收端芯片管腳處測試分析信號還有意義嗎?力科眼圖醫生EyedoctorII軟件可以 為您解決這些問題。

圖3 帶有預加重和均衡的高速信號測試

二、典型的高速信號設計的主要步驟

由于當前工藝水平越來越高,信號速率高于5Gbps的信號標準已經越來越多,如PCIE2.0達到5Gbps,8Gbps的PCIE3.0標準也可能很快 就會推出;USB3.0達到5Gbps,SATAIII達到6Gbps等等。信號速率的進一步提高對電路設計工程師也提出了更多嚴格的要求;

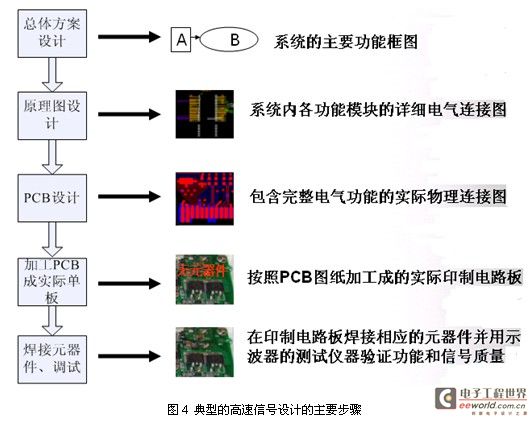

一個典型的硬件系統設計流程大概包括五個步驟:即總體方案設計:主要完成系統的功能框圖、原理圖設計:主要完成系統內各功能模塊的詳細電氣連接圖、 PCB設計:主要完成系統內各功能模塊的電氣連接圖、加工PCB版圖為尚無元器件的實際單板、最后焊接好元器件進行功能信號等的調試和測試,如圖4所示。

在過去低速系統中,通常只在硬件系統設計流程的最后一步進行測試驗證來保證達到基本功能要求。而對于高速系統來說,要求會大大不同,第一個不同是需要在設 計的更早階段就要進行信號質量的分析,通常在硬件系統設計流程的第三步即已經完成PCB版圖設計但尚未投板之前就進行嚴格的信號完整性分析;第二個不同是 不僅僅是需要滿足功能測試的要求,而且是每個高速信號在滿足要求之外還需要較大的余量,以確保高速信號乃至整個系統的高可靠性。對于5Gbps以上的信 號,還有個不同是有些標準中已經明確提出需要對接收端的進行容限測試,如USB3.0,而以往接收端測試只是選項測試。

三、典型的高速背板系統及其主要設計調試流程

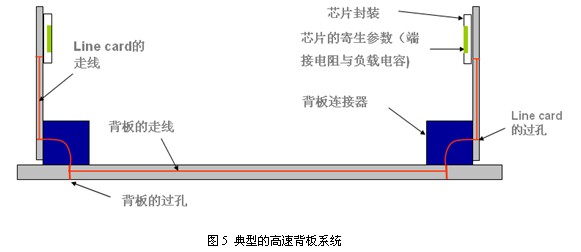

下面我們以一個高速背板系統為例來說明下高速系統的設計流程。如圖5所示為一個典型的由兩個線卡加上一塊高速背板構成的高速信號傳輸系統。我們看到,圖最 下方的為帶有高速接插件的背板,通過接插件在左右各有兩個線卡(line card)插在背板上,左邊的線卡上有高速信號發送芯片,右邊的線卡上有高速信號接收芯片,如圖中紅色線所示,高速信號從左邊子卡上的發送端芯片發出,經 過線卡上的傳輸線、接插件、背板上的走線、接插件、線卡上的傳輸線到達芯片接收端。子卡上的高速信號走線通常比較短,對信號的影響很小;背板上的走線都比 較長,對信號影響最大,背板面積通常都比較大,生產成本也比較高,所以對于這樣一個系統來說,背板設計的成敗將至關重要;這樣一個系統設計的主要挑戰在于 如何有效的解決背板傳輸線對信號質量的影響(如阻抗不連續帶來的反射問題、走線過長帶來的信號幅度過度衰減問題、高速信號的ISI問題、板間連接處的阻抗 連續性問題)。當然選擇好芯片、接插件、PCB板材等也是很重要的因素。此類問題都可以通過仿真方法與測試方法相結合來更好的解決。

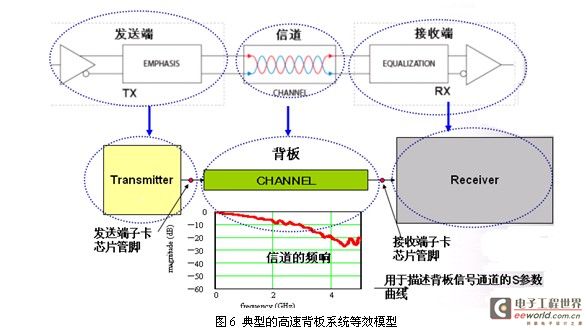

將上頁的高速背板系統作一個等效的模型,如圖6所示,由于線卡上走線較短,所以我們把發送端和接收端線卡簡化,以發送端Transmitter和接收端 Receiver表示,通常發送端帶有預加重,接收端帶有均衡;背板上的長傳輸線主要用于傳輸信號,通常稱為信道,即傳輸信號的通道,在SI類的文獻中也 稱為互連,可以用S參數模型來等效其信道的響應。S參數模型可以通過VNA測試或者電磁場、CAD等仿真軟件仿真得到。

對于當今的高速系統設計來說,需要在更多的設計環節進行信號質量控制,對于上述的典型高速背板系統來說,一般有如下三個環節:(1)子卡、背板的PCB版 圖已經完成(子卡指發送端子卡和接收端子卡);(2)子卡已經加工完成,背板的PCB版圖已經完成但是尚未加工;(3)子卡和背板的PCB版圖已經完成;

對于第一個環節,即子卡、背板的PCB版圖已經完成,則主要是通過軟件仿真的方法。如使用HSPICE軟件將發送端和接收端芯片的HSPICE模型和背板 的S參數模型整合到一起進行通道仿真。此一環節進行分析的優點是目前只有電路設計圖紙,還未做成實物,如果此階段發現問題,則可以方便的修改調整設計,不 會造成大量成本損失;而且必將大大縮短產品研發周期,節省時間;缺點是需要芯片廠家提供精確的HSPICE模型(有時候得到這樣的精確模型比較困難);仿 真軟件所使用的信號源為理想信號源,未考慮子卡上的實際情況如串擾、反射等等,而且目前的高速仿真軟件仿真速度比較慢,會大大影響調試效率。

評論