數字電視信號發生器原理及設計-FPGA設計篇

如何選擇自己理想的數字電視產品,也成了消費者關心的問題,評價、測試電視系統與設備運行的質量狀況成為廣播電視行業所關注的熱點。

本文引用地址:http://www.104case.com/article/201612/334353.htm 而數字電視信號發生器能提供可視的測試圖像信號,直觀、快捷的測試方法,因此,數字電視信號發生器成為目前電子設計的熱門研究課題,他在數字電視節目制作播出、科研、生產以及售后服務過程中起著不可或缺的作用。

數字電視信號發生器的功能與原理

1、系統功能

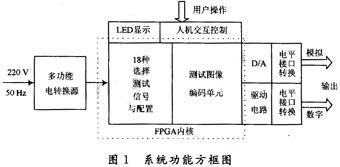

數字電視信號發生系統的主要任務是產生符合SMPTE274M系統標準的18種數字信號測試圖像,YPbPr,RGB兩種視頻輸出接口符合ITU-RBT.1120-2/GY/T157-2000演播室高清晰度數字視頻信號接口標準。本系統的核心是圖像信號的編碼發生單元FPGA,采取單芯片多配置方案可使18種圖像信號方便地進行配置與加密。人機界面由單片機控制,可快速地進行圖像切換和格式轉換。在普通電源接入下,系統需生成支持SMPTE274M系統標準中的1080I60Hz,1080I50Hz,1080P60Hz、1080P50Hz四種標準格式的18種高清晰度電視通用測試圖像的數字輸出信號和模擬輸出信號,其標準測試信號的數碼發生內核基于FPGA平臺實現。在此基礎上,本系統提供了一個人工可控功能,即用戶可根據按鍵,對以上4種標準的18種測試圖案進行切換控制。考慮到輸出信號的實用性,輸出的模擬測試信號和數字測試信號都必須滿足相應的接口標準。為滿足以上約束條件,系統功能設計如圖1所示。

2、信號產生的原理

數字電視也是彩色電視(只是信號的表示形式及信號的處理方法與模擬電視有所不同),因此在考慮數字電視測試信號發生器包含哪些(測試信號)內容時,本文根據彩色電視的基本特點,首先應考慮包含一般彩色電視廣播測試圖的基本內容,例如觀察顯示設備掃描非線性失真和幾何失真的棋盤信號和圓信號,觀察圖像清晰度和分辨率的多波群或掃頻信號,觀察亮度非線性失真情況以及顯示器白平衡調整是否正確的灰度級(或階梯波)信號,觀察彩色重現是否正確的彩條信號等;另外還考慮增加了在視頻測量中最常用的2T脈沖信號、彩色多波群信號和彩色階梯波信號,以及更為直觀的斜波信號等,以便全面地觀察和評價彩色電視系統或設備的基本質量。

數字電視信號發生器的FPGA設計

1、FPGA設計原理

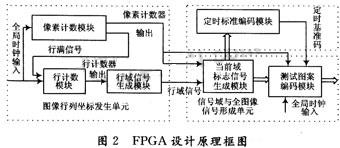

FPGA是整個數字電視測試信號發生器系統的核心,各種測試信號編碼都在這一部分實現。FPGA設計原理如圖2所示。

所有測試信號的編碼均基于圖像的行/列坐標而產生,其行坐標和列坐標分別為像素計數器和行計數器根據全局時鐘上升沿進行計數所得數值。行域信號生成模塊對行計數器輸出的值進行閾值劃分,將測試圖像按行劃分為不同的區域,稱為行域。在不同的行域中,根據像素計數器值進行不同的像素區域劃分,將測試圖像進一步劃分為相對獨立的信號編碼區域,每個區域對應一個標志信號。此時,行/列坐標與信號編碼區域一一對應,稱當前輸出信號所在行/列所對應的信號編碼區域為當前域,其標志信號為當前域標志信號。最后,根據當前域標志信號對測試信號的定時基準碼、有效區域等信號進行編碼,由測試圖案編碼模塊輸出全圖像信號數字視頻分量的碼值。

2、FPGA設計總體結構

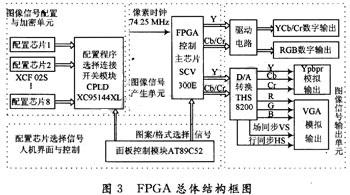

該模塊是系統工作的核心,如圖3所示,單芯片多配置方式中的主芯片,可提供支持SMPTE274M1080I60Hz/1080I50Hz格式的18種高清電視通用測試圖,如綜合測試卡信號、SMPTE219-2002測試圖、SMPTE198-1998場檢測圖等。主芯片根據控制模塊輸出的圖案/格式選擇信號,選擇不同的配置程序,輸出相應測試圖的數字Y、Cb/Cr信號碼值,以及相關的同步/消隱控制信號。

2.2.2圖像信號配置與加密單元

該模塊由8片配置芯片XCF02S與1片XC95144XL組成,是成功實現單芯片多配置方案的關鍵模塊。配置程序選擇連接開關即根據控制模塊輸出的5b配置芯片選擇信號,選擇相應測試圖案的配置芯片PROM的系統可編程JTAG連線與主芯片對應引腳相連接。

2.2.3圖像信號輸出單元

數字輸出部分由驅動電路與接口芯片組成,模擬輸出部分由TI公司的D/A轉換芯片THS8200及其內部IFIR數字濾波器以及外圍運算放大器電路實現數模轉換功能。可根據控制模塊的圖案/格式以及模擬輸出接口類型選擇信號,將Y、Cb/Cr的并行數字視頻分量信號轉換為模擬輸出,或者轉換為RGC模擬輸出。

2.2.4人機界面與控制單元

控制模擬信號輸出類型,并通過輸出I2C總線對D/A轉換芯片的寄存器進行相應配置。根據外部輸入信號,產生相應的圖案/格式選擇信號和配置芯片選擇信號,控制主芯片與配置芯片的斷電與上電時序,與選擇連接開關模塊共同完成測試圖切換功能。這種單片多配置方案,信號轉換速度很快,與單片單配置方案一樣,為毫秒級。

2.3FPGA測試圖像信號產生

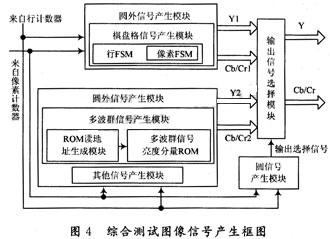

綜合測試圖像信號實際上是由多種測試信號合成的,包括圓信號、棋盤信號、多波群信號、彩條信號等。設計將綜合測試圖分為三個層次實現。第一層設計采用圓信號作為選通信號,圓信號外的視頻有效區域輸出棋盤信號,而圓信號內的視頻有效區域輸出多種測試信號;第二層設計采用行計數器值作為信號劃分邊界值,不同的行域輸出不同的測試信號,用于測試設備的各種性能;第三層設計采用像素計數器值作為信號內部的區域劃分參數,完成每種測試信號的生成。其代碼設計基本框圖如圖4所示。

其中圓外的棋盤信號采用灰底白格棋盤,圓內信號從上至下依次設計為白場、信號、2T脈沖信號、黑白場交織信號、100%彩條信號、亮度多波群信號、6電平亮度五階梯信號、2T脈沖信號與色亮時延差觀察信號。其中黑白場交織信號中黑場與白場交替出現,每場寬80個像素點;彩條信號電平符合100/0/100/0,每個彩條信號寬160個像素點;亮度多波群信號每波帶信號寬160個像素點;6電平亮度五階梯信號每階梯寬160個像素點;2T脈沖信號為半幅值寬度為34ns、幅度為80%視頻幅度的2T正弦平方正脈沖和負脈沖信號;根據黃、紅色亮度電平相差較大及便于觀察等因素,色亮時延差觀察信號采用黃、紅信號,其紅黃交界處與其上面的2T脈沖峰值點在測試圖中的水平方向位置相一致。為有效利用FPGA資源,并縮短開發周期,綜合測試圖中的多波群信號直接調用ROM的IP核實現。

評論