運用示波器和用戶可定義的 FPGA 提高測量質(zhì)量與速度

1. 什么是「軟件設(shè)計的示波器」?

示波器等儀器通常采用多個軟件層,有些是用戶較容易存取的軟件,有些則否。 PC 上的軟件可控制測試系統(tǒng)的整體運作,儀器驅(qū)動程序可提供示波器的通訊功能,嵌入儀器本身的軟件則控制了數(shù)據(jù)采集和提供給用戶的方式。 傳統(tǒng)儀器會通過儀器驅(qū)動程序提供固定的測量功能;模塊化儀器則運用了開放式的 PC 軟件和現(xiàn)代 CPU 的處理性能,可以在 PC (而非儀器內(nèi)部) 執(zhí)行訊號分析。 這樣一來,用戶即可迅速定制針對采集到的數(shù)據(jù)執(zhí)行數(shù)據(jù)分析的方式,以此滿足個人的特殊需求,例如縮短測試時間或提高測量分辨率。

本文引用地址:http://www.104case.com/article/201612/333314.htm軟件設(shè)計儀器進一步運用這個概念,可供用戶修改或甚至徹底替換儀器 FPGA 上所執(zhí)行的嵌入式軟件。 因為每個采集到的數(shù)據(jù)點都可以實時在儀器 FPGA 上完成分析,所以用戶可實現(xiàn)定制的實時分析和復(fù)雜的觸發(fā),并且避免空滯時間 (錯失訊號)。 簡而言之,軟件設(shè)計儀器能夠讓用戶存取所有的軟件層,從主機 PC 到儀器數(shù)據(jù)轉(zhuǎn)換器的針腳全都包含在內(nèi),進一步實現(xiàn)定制的修改內(nèi)容,滿足特定的應(yīng)用需求。

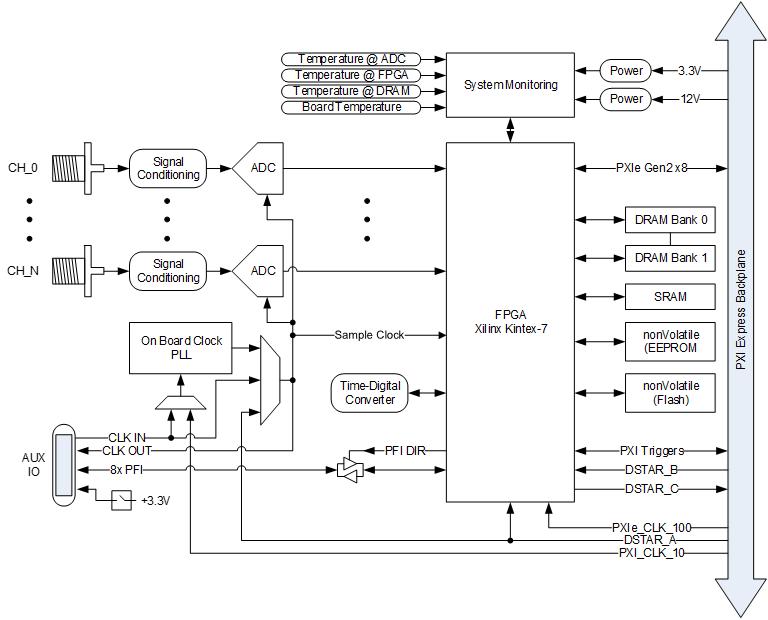

全新 NI PXIe-5171R 示波器是一種軟件設(shè)計儀器,配備 8 個輸入通道、300 MHz 模擬帶寬、250 MS/s 取樣率、14 位分辨率,以及用戶可設(shè)定的 Xilinx Kintex-7 FPGA。

圖 1: 用戶可定義的 FPGA 作為軟件設(shè)計儀器 (PXIe-5171R 示波器) 程序框圖的核心組件。

2. 透過軟件來設(shè)計示波器 FPGA 的程序

LabVIEW FPGA Module 能夠把 LabVIEW 系統(tǒng)設(shè)計軟件擴充至 NI 可重設(shè) I/O (RIO) 硬件上的 FPGA;而這類硬件則包含了 PXIe-5171R 和 PXIe-5624R 示波器、數(shù)字序列儀器、RF 向量訊號分析器,以及在 2012 年發(fā)表「軟件設(shè)計儀器」概念的向量訊號收發(fā)器 (VST)。

LabVIEW 本身即具有平行機制,而且數(shù)據(jù)流概念和 FPGA 的數(shù)據(jù)流也很像,因此非常適合用來設(shè)計 FPGA 程序。 LabVIEW 能夠抽象化系統(tǒng)內(nèi)不同操作部分所執(zhí)行的處理和數(shù)據(jù)遷移作業(yè) (例如儀器內(nèi)的 FPGA 和 PC 內(nèi)的微處理器),因此工程師和科學(xué)家不需要 Verilog 或 VHDL 之類的 FPGA 程序設(shè)計、運算架構(gòu)或數(shù)據(jù)串流等方面的深入知識,即可充分發(fā)揮軟件設(shè)計儀器的性能。

LabVIEW 本身即具有平行機制,而且數(shù)據(jù)流概念和 FPGA 的數(shù)據(jù)流也很像,因此非常適合用來設(shè)計 FPGA 程序。 LabVIEW 能夠抽象化系統(tǒng)內(nèi)不同操作部分所執(zhí)行的處理和數(shù)據(jù)遷移作業(yè) (例如儀器內(nèi)的 FPGA 和 PC 內(nèi)的微處理器),因此工程師和科學(xué)家不需要 Verilog 或 VHDL 之類的 FPGA 程序設(shè)計、運算架構(gòu)或數(shù)據(jù)串流等方面的深入知識,即可充分發(fā)揮軟件設(shè)計儀器的性能。

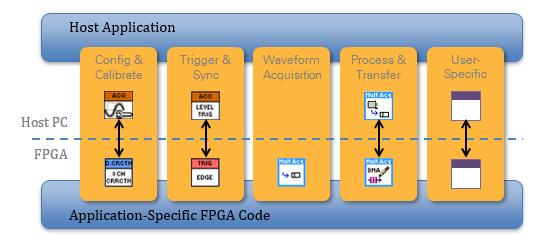

圖 2 為軟件設(shè)計儀器的軟件架構(gòu) (目前以示波器為例)。 此架構(gòu)包含了實現(xiàn) FPGA 的例程,可用于實際采集和實時處理,以及主機 PC 上對應(yīng)的軟件模塊,能夠和 FPGA 上的對應(yīng)部分互動,進一步設(shè)定/控制測量作業(yè)、處理 PXI Express 總線的數(shù)據(jù)傳輸,并且呈現(xiàn)數(shù)據(jù)給用戶。

圖 2: 就軟件設(shè)計儀器的架構(gòu)而言,主 VI 會和 FPGA 上的對應(yīng)部分互動,以此設(shè)定硬件并執(zhí)行測量。

主機 PC 的組件和儀器驅(qū)動程序很類似,F(xiàn)PGA 程序代碼則是和傳統(tǒng)的示波器硬件比較像。 不同于傳統(tǒng)示波器,這些組件可用來建置定制示波器 IP,同時也因為開放式特性,可供用戶根據(jù)特定需求而修改或擴充

3. 示波器搭配用戶可定義的 FPGA 所提供的測試優(yōu)勢

測試應(yīng)用的終極目標之一就是縮短整體的測試時間。 時間通常是提高大量制造成本的主要原因之一,彈性和可重復(fù)使用率對高度混合或高度維護測試系統(tǒng)而言則是非常重要。 下列三個范例說明了示波器搭配用戶可定義的 FPGA 如何節(jié)省時間和成本。

在線處理和 DUT 控制,加快測量速度

許多應(yīng)用必須透過通過數(shù)字濾波、信道化、快速傅立葉變換 (FFT) 或解調(diào)等措施來處理所采集的數(shù)據(jù)。 雖然現(xiàn)代的多核心 CPU 可提供無與倫比的處理性能給桌面計算機,但通常無法實時處理多核心示波器所產(chǎn)生的數(shù)據(jù),所以也沒辦法快速執(zhí)行測量作業(yè)。 結(jié)果就是 CPU 會成為測試速度的關(guān)鍵。 有了 FPGA 和固有的平行機制,即可輕松持續(xù)執(zhí)行復(fù)雜的分析作業(yè),例如實時并行計算多個通道的功率頻譜。

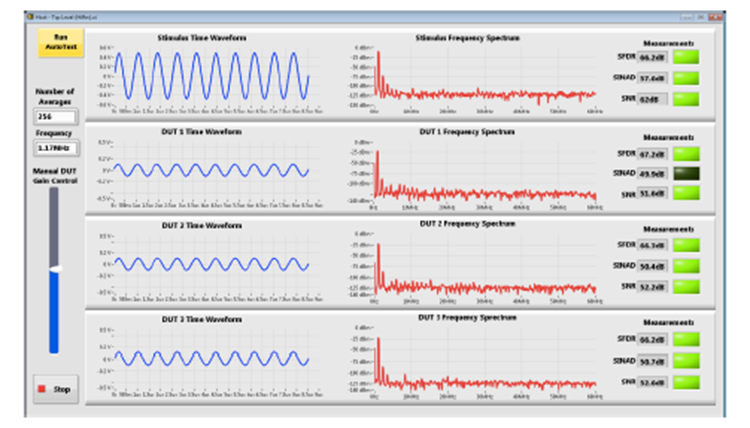

圖 3 為用戶可定義的 FPGA 如何用于 PXIe-5171R 示波器,只要一次就能采集并測量一個 DUT (RF 切換器) 內(nèi)多個通道的串音。 4 個示波器通道會平行采集 DUT 所有 4 個信道的輸出訊號,計算所有 4 個通道的功率頻譜,并且針對違反情況執(zhí)行屏蔽測試。

圖 3: PXIe-5171R 示波器搭配用戶可定義的 FPGA,可執(zhí)行平行的頻譜測量,進而縮短測試時間。

另一個在線處理的例子就是透過 DUT 關(guān)閉循環(huán)。 示波器本身可控制 DUT 并縮短測試時間,而非由主機 PC 來控制測試系統(tǒng)內(nèi)的 DUT 和示波器 (這樣會帶來通訊時間的運作成本)。 示波器的 I/O 通道可做為分離式 I/O 使用,也可當作 SPI 之類的序列總線,以便和 DUT 通訊。

圖 4: 測試高速數(shù)字轉(zhuǎn)模擬轉(zhuǎn)換器 (DAC) 的刺激反應(yīng)系統(tǒng)。

透過點對點數(shù)據(jù)流技術(shù),示波器即可結(jié)合其他儀器,打造出閉循環(huán)測試系統(tǒng) (圖 4)。 示波器內(nèi)部的 FPGA 會產(chǎn)生測試訊號,并且傳送至數(shù)字序列儀器,以此驅(qū)動 DAC 輸入。 示波器會采集頻譜,并且自動比較采集到的訊號和預(yù)期的訊號 (也就是之前產(chǎn)生的訊號)。

透過自定義觸發(fā)和協(xié)議解碼縮短測試時間

對許多測量作業(yè)而言,偵測特定的訊號狀況以啟動采集作業(yè)是相當重要的功能。 傳統(tǒng)的示波器可以精確采集一些觸發(fā)狀況 (例如某個訊號超過臨界值),但因為儀器處理已采集的資料而帶來的空滯時間,所以無法每次都偵測到更復(fù)雜的事件,例如脈寬。

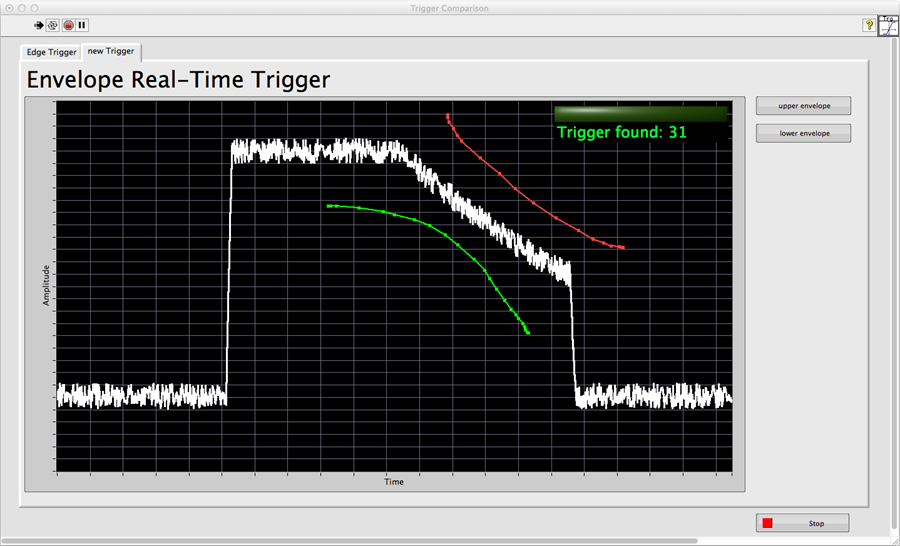

用戶可設(shè)定的 FPGA 可做為訊號鏈不可或缺的一部分,并且針對用戶定義的狀況實時分析每個訊號。 這樣一來即可以精確穩(wěn)定的方式,偵測簡易 (準位和磁滯) 和復(fù)雜觸發(fā),例如訊號抖動或脈寬、特定上升時間,或甚至特定的訊號形狀。 圖 5 的觸發(fā)狀況運用了一個訊號封包,以此觸發(fā)采集作業(yè)。 諸如此類的觸發(fā)情境可用于設(shè)計和測試項目,以便偵測單邊緣觸發(fā)器難以偵測到的異常行為。

圖 5: 特定訊號形狀引發(fā)的觸發(fā)。 在此范例中,訊號必須介于紅色和綠色曲線之間,才能夠觸發(fā)采集作業(yè)。

此外,也可以組合多個觸發(fā)器,進而偵測復(fù)合狀況,例如可以在不同通道上看到特定頻譜內(nèi)容的數(shù)字樣式,或者是一連串的事件,通常稱為 A-B 觸發(fā)器。

有個相關(guān)功能就是可根據(jù)序列通訊接口上的特定數(shù)據(jù)字詞或錯誤,偵測并觸發(fā)采集作業(yè)。 有了用戶可定義的 FPGA,即可測試訊號的完整性 (根據(jù)規(guī)格測試訊號的模擬波形),同時平行譯碼輸入數(shù)據(jù),以此驗證數(shù)據(jù)內(nèi)容。 這樣一來,用戶不但可以測試訊號,也能夠建立可做為最終系統(tǒng)組件并快速制作原型的測試設(shè)定,有效運用單一儀器同時完成兩項工作。

仿真舊設(shè)備以減緩產(chǎn)品汰換問題

軍事或航天應(yīng)用領(lǐng)域內(nèi)許多維護測試系統(tǒng)都有使用壽命的需求,可延長至 10 年以上。 通常會根據(jù)特定的儀器特性而撰寫測試程序代碼 (無論是否刻意),因此很難在避免大幅變動的情況下替換儀器,而且重新認證測試程序代碼也需要高額的成本。

用戶可定義的 FPGA 可供程序設(shè)計,藉此修改儀器并仿真遭替換設(shè)備的行為,有助于避免上述問題。 運用 FPGA 邏輯即可輕松復(fù)制觸發(fā)行為或時序組合等特性,此外只要透過數(shù)字方式實作所需的濾波器,甚至可以模擬更復(fù)雜的方面,例如示波器的濾波特性。

4. 示波器搭配用戶可定義的 FPGA 所提供的科學(xué)應(yīng)用優(yōu)勢

就高能物理等科學(xué)應(yīng)用而言,儀器的性能與彈性都是很重要的特色。 一般來說,這類應(yīng)用大部分的訊號處理和控制作業(yè)都會采用模擬電子和相對較慢的 ADC,以此采集預(yù)先處理過的訊號。 現(xiàn)在,快速的高分辨率 ADC (14 位和 250 MS/s 以上) 可直接從傳感器采集訊號樣本。 只要儀器搭載用戶可設(shè)定的 FPGA,即可在采集期間同時執(zhí)行訊號處理作業(yè),不必通過 PC 完成后續(xù)處理。 這樣不但可以更快取得結(jié)果,也能夠提高科學(xué)實驗控制的彈性和效率。

有效實時反饋系統(tǒng)的在線處理

許多科學(xué)實驗都必須仰賴控制系統(tǒng),確保所有設(shè)定項目都維持在明確定義的狀態(tài)。 舉例來說,DIII-D Tokamak 等融合研究系統(tǒng)會透過 RF 功率來加熱等離子體,這會需要測量復(fù)雜的 RF 反射系數(shù),并且根據(jù)測量結(jié)果衍生出合適的控制參數(shù)

使用粒子加速器和同步加速器時,必須持續(xù)監(jiān)控粒子光束的軌跡,才能滿足磁鐵的正確控制輸入需求。 示波器搭配用戶可定義的 FPGA,提供了固有的快速平行處理性能,能夠同時分析訊號和頻域,以及極高速的控制循環(huán),因此有助于解決 DIII-D Tokamak 等應(yīng)用問題。 只要客制化 FPGA,即可監(jiān)測重要的安全參數(shù),以便在系統(tǒng)處于非理想狀態(tài)時觸發(fā)關(guān)機作業(yè)。

示波器可透過高速 PXI Express 總線,搭配輸出模塊以產(chǎn)生實驗所需的控制訊號,或是以每個儀器超過 3 GB/s 的速度連續(xù)把數(shù)據(jù)串流至儲存媒介。 用戶可定義的 FPGA 還有另一個優(yōu)點,那就是可以快速修改處理和控制算法。 可以把已編譯過的位串流加載 FPGA,只要不到一秒的時間,即可改變示波器的行為。

實時事件偵測和數(shù)據(jù)減量,有助于加速探索

判斷重點事件通常相當困難。 常見的作法就是等到實際數(shù)據(jù)采集作業(yè)結(jié)束之后,在后續(xù)處理期間尋找事件,不過這么做很花時間,而且必須儲存大量的數(shù)據(jù)。

另外有一個更有效的方式,就是在采集期間決定要保留和舍棄的訊號,以此把數(shù)據(jù)量降到最低。 通常唯一的重點參數(shù)就是時戳和能量脈沖的計算結(jié)果,所以就儲存觀點而言,從儀器回傳這些參數(shù)會更有效率,而且因為采集到的結(jié)果可輕松卸除至主機 PC,所以還可以延長測量時間。

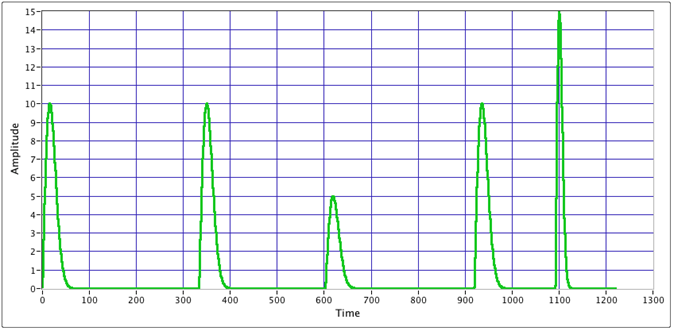

舉例來說,飛行時間 (ToF) 應(yīng)用會持續(xù)繪制粒子和能量。 如圖 5 所示,較快的粒子位于左邊 (飛行時間較短),較慢的粒子則位于右邊。

圖 5: 標準的 ToF 圖和偵測到的脈沖,這些脈沖會傳輸至主機 PC。

測量系統(tǒng)的功用在于采集、時戳、測量能量脈沖,并且排除時間 (采集到的數(shù)據(jù)),中間完全沒有脈沖,通常稱為零點抑制。 透過 FPGA 即可輕松實作,因為可以實時計算每個樣本。 如圖 5 所示,偵測事件的一般架構(gòu)可能會是脈沖 (例如某個臨界值) 偵測器,接著是符合已偵測脈沖上參考脈沖 (例如高斯形狀) 的算法,以便估計最大值。 偵測峰值和對應(yīng)時戳并加以儲存之后,即可舍棄所采集到的脈沖,也可傳送至另一個緩沖區(qū),以便進一步分析或于 PC 顯示。

LabVIEW FPGA 提供一些工具給用戶,能夠把必要的訊號處理階段實作于示波器上,藉此執(zhí)行脈沖過濾和整形、計算出現(xiàn)次數(shù)并加上時戳、測量高度和上升時間、直接在儀器內(nèi)重新建構(gòu)基線,并且把壓縮過的結(jié)果回傳至 PC,以便提高研究人員的工作效率。

5. 結(jié)論

傳統(tǒng)示波器的原理是基于對信號進行快照的模式,然后在采樣的后端將采到的信號對齊現(xiàn)實給客戶波形測量。這樣的方式會丟掉兩次快照之間的數(shù)據(jù),如果我們需要尋找一個信號中很小概率的細節(jié),那傳統(tǒng)儀器無疑會增加很多的測試時間。并且,基于FPGA將所有信號無縫采集,可以進行實時的信號處理,比如找出特定的信號波形,將其觸發(fā)。與傳統(tǒng)的示波器只能基于電平的觸發(fā)方式不同,全新的可重配置示波器可幫助用戶透過定制化觸發(fā),更快偵測事件,并且實時處理數(shù)據(jù),直接透過儀器把數(shù)據(jù)轉(zhuǎn)換成結(jié)果,進一步提高測量質(zhì)量與速度。

評論