實現高速串行I/O效率的嵌入式測試

隨著技術的進步,電子產業自身在不斷地發明創新。嵌入式系統設計師相當清楚這一點,許多人開發的應用數量甚至可以橫跨幾代電子技術和微處理器技術。

本文引用地址:http://www.104case.com/article/201612/333223.htm一路看過來,隨著基本的硬體和軟體的演進,當然也出現了許多不同的系統開發和除錯方法。如今,絕大多數微處理器整合有晶片上除錯資源,因而設計師可以利用低成本的硬體介面進行開發和測試。這類被稱作為嵌入式測試的除錯,大幅有助于嵌入式系統的成長,并將使具有高速串列I/O的設計系統具有更高的效率。

如今,半導體硅晶片成本的降低使得電子產業可以利用通訊產業30多年發展所取得的一些先進技術,特別是串列介面。就當數位系統拼命地與大規模、高速數據傳輸的光系統的處理頻寬保持同步時,前所未有的對速度和總處理吞吐率的需求激勵了平行匯流排結構針對其自身的一些實際限制進行演進,為了獲取更高的處理頻寬,PC領域正鐘情于高速串列介面,向PCI-Express這類匯流排標準的迅速成長就是例證。

由于PC領域採用了串列介面,這些技術正被廣泛接受并確立地位。實現成本開始下降,這就意味著目前串列介面正邁上低成本的PC產品和主流數位產品──換言之,即嵌入式系統之路。我們將再一次看到該演進過程:即隨著嵌入式系統和相關的處理器採用該項新技術,設計團隊必須採用新的開發和除錯方法來利用高速串列埠的優點。

採用新測試方法

如今,絕大多數的數位電路設計師還習慣于採用平行介面和速率為100~200MHz左右的系統時脈。的確,有很好的標準,又有熟知的經驗和工具支援這類選擇。但是,高速(數Gb)串列完全是另外一回事。如今,成功配置高速串列介面的設計團隊通常聘用在高速訊號傳輸(訊號完整性)的實體層方面具有特殊經驗的工程師。由于該方案將有助于將產品成功地投入市場,故需對開發團隊進行較多的改變,以便于將這一先進的技術整合進針對主流數位電子產品市場的設計中去。開發團隊需要更有經驗的設計師,以及所需的設計工具和設計方法,來解決與以往大不相同的設計問題。

第一步是要瞭解設計問題。如何設計與過去大不相同的數位高速串列介面?可能最大的差別在于訊號完整性。由于這些主要介面的訊號速率都高達Gb,將會出現許多通常只有類比(或者更像是RF/微波)領域才會出現的問題。設計師這就不像過去那樣只需關注像設立時間、保持時間和上升時間這類的訊號定時參數,而是必須關注像視圖張開、位元誤差率和抖動的參數。

另一個不同之處在于探測設計師希望觀測的訊號的能力。該功能無論是對于目前的半導體的高整合度,還是細心地調理訊號通道上的訊號完整性都不可或缺的。隨著速率上升到3Gbits/s,就需要對訊號進行一些先行傳輸調理,來補償傳輸媒質的耗損;接收端的訊號處理也需要相應的濾波,來精確地恢復訊號。同樣,由于有些訊號通常都工作在次微米數位硅晶片的低功率環境,電壓的擺幅較小。這意味著傳統的測試測量方法,即簡單地利用實體探頭來進行接觸式探測將變得不太可能,因為探頭自身將會對訊號帶來很大程度的影響。

測試和除錯這些介面時必須考慮到這些因素所產生的實際影響。對數位完整性方面的需求意味著數位設計師必須在驗證設計所用的標準工具庫內添加新的測量類型(或測試設備)。目前,測量訊號完整性的復雜設備正普及,并且隨著從以前的特定應用發展到主流應用的過程中還必須不斷演進,這些設備包括視圖測試、位元誤差率(BER)測試以及抖動容差測試設備。隨著這些訊號變得更加靈敏,半導體硅晶片的整合度變得更高,為了能夠探測這些關鍵訊號,這些測試解決方案還必須不斷演進。

解決方案是嵌入式測試

如同微處理器領域中的晶片上除錯工具和技術的出現一樣,解決方案應該是在硅晶片上實現更多的測試功能,至少對于探測問題是如此。由于晶片開發商非常仔細地設計了訊號通道,故對于應用設計師來說,整合能力并利用這種方法來進行關鍵測量和觀察串列埠的行為將是最好的方法。這種稱作為嵌入式測試的方法,不需要外觸探頭(探頭自身將引起相關的問題),而且可以獲取外部無法獲取的訊號的相關資訊(例如被接收機恢復實際視圖指標)。

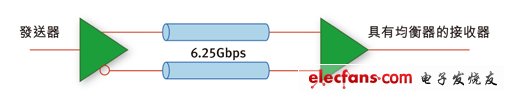

圖1(詳見本刊網站)提供了一個實際例子。這?堙A在速率為6.25Gbits/s的串列鏈路上進行的測量顯示,即便實體探頭的限制可以克服,在元件接腳上觀察訊號也將導致錯誤的結果,由于採用了先行傳輸訊號調理。如果只是簡單地看一下圖示的資訊,人們可能會斷定該鏈路無法工作,因為觀察不到訊號視圖的張開。但是,透過結合晶片上測量,如圖中的右側所示,工程師就能夠確信確實有一個訊號被接收機恢復了。

圖1:高速串列鏈路測試的實際例子。

FGPA的用途

隨著串列技術在嵌入式系統中的出現,FPGA將扮演一個重要的作用。長期以來FPGA都是嵌入式設計師使用的實現技術,而隨著FPGA性價比的演進,其作用正增加。FPGA正日益增多地成為一個整合平臺,它具有類似晶片上系統(SoC)的功能,而這些功能則利用可編程的架構來實現。這為嵌入式系統設計師帶來了頗多的靈活性,并使他們能在其設計中以低成本的方案實現高整合度。

FPGA供應商也意識到了正轉向串列埠的這一趨勢,并正致力于為更多的開發商提供可用的高速串列技術。絕大多數的高階FPGA產品中目前都有數Gb的串列I/O功能,該功能也正開始進入低成本的FPGA元件中。FPGA固有的可重新編程能力還為實現測試功能的測試工具提供一個真正的機會。開發和測試工具正涌現出來,這為設計師提供了掌握串列介面的行為和品質的新方法。這些新工具採用與高速串列技術指標(如BER測量)相關的測試類型,這就使得它們對以前由于知識面和採購相關儀器成本所限而沒有考慮過的各類設計師來說都是有用的。

測試FPGA中的高速串列I/O

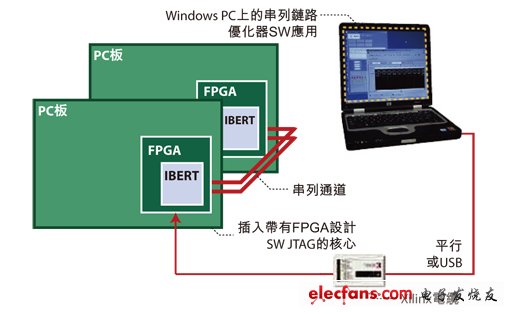

這些工具可用來時FPGA開發商測量串列I/O。圖2為此類工具架構圖。

圖2:用于高速串列鏈路測試的嵌入式測試解決方案架構圖。

該工具有叁個基本的部份組成:

1. 實現晶片上測試模式產生、BER測量和存取發射和接收器控制記憶體的測試核心;2. 測量軟體;3. 簡單的硬體介面,本例中用JTAG編程電纜來實現。

人們可以看到,利用該架構,透過適當地配置這叁個部份,就可以設立起一個測量例程來探測用Xilinx FPGA實現的高速串列鏈路工作情況。

這樣的測試工具提供了進行叁個基本鏈路測量的能力,所有的都基于BER,其已被廣泛地接受作為高速串列埠的最終測量。最簡單的就是該工具可以提供鏈路BER測量。該測量在內部實現,并反映從FPGA內部的接收器所視的實際條件,而無須採用傳統測量中通常使用的接觸式探頭來測量元件的接腳。

另一個感興趣的測量是視圖測試(圖3詳見本刊網站),這為迅速掌握鏈路裕度提供了一個簡單的方式。透過在數據眼的單位間隔上重復進行BER測量,可以為用戶提供BER與數據眼位置關係的圖形顯示。最終,透過將視圖測量功能與發射和接收控制暫存器存取相結合,就能有效地對鏈路進行調整,來獲得最佳的BER。

圖3:能夠測量鏈路裕度的視圖測試。

嵌入式測試的內涵

嵌入式系統中對串列I/O的採用將對如何成立設計團隊和採用什么工具產生影響。我堅信針對這一技術的嵌入式測試的特殊應用將為開發商帶來有價值的幫助。在高速串列領域及以外的其它領域許多其它的可能性都與這一概念相關。很顯然,隨著半導體技術在復雜度和功能以及速度等方面的不斷發展,嵌入式測試方案將為系統設計師探究系統提供真正的機會,不論是硬體還是軟體。

實現嵌入式測試要求一定的靈活度,以便將全新的測試拓樸架構和新的測試方案整合在一起來實現跨度覆蓋到半導體製造商和測試測量供應商的測試解決方案。儘管這些合作意味著將對產業帶來挑戰,但卻能為位于競爭的價值點上的設計師帶來全新的、具有價值的測量功能,這都將是不可否認的經濟驅動力。

評論