LVDS已淘汰?LVDS和JESD204B將繼續長期發展

前些年,LVDS(低壓差分開關)開始逐漸取代CMOS。 而如今,JESD204B也顯現出類似的發展趨勢。

CMOS I/O接口包含單獨的單端邏輯信號。 LVDS將這些單端邏輯信號轉變為180°反相(從而是差分)信號線路對。 差分信號可產生更高的抗干擾能力,因此通常能夠以更低功率水平工作,以實現等效信噪比。 JESD204接口標準針對通過串行鏈路發送和接收數據,通常是從ADC至FPGA或ASCI。 其它修訂版本則闡述時鐘和多個數據信號路徑(“通道”)相關內容,以及通道同步問題。 顯然,系統設計人員似乎不愿意對轉換器與FPGA或ASIC之間的接口做出這么大的改變。 畢竟,這需要修改設計,不是嗎? 人們理所當然地認為做出改變應該很容易。 縱觀大局,改變需要進行工程設計,需要付出時間和金錢。 然而,隨著技術的不斷進步以及系統帶寬要求越來越高,同樣必須進一步提高轉換器的采樣速率。 這就使得LVDS將不再適用。 雖然LVDS的電流和功耗依然相對較為平坦,但接口的最高速度受到了限制。 這是由于驅動器架構以及許多數據線路都必須與某個數據時鐘同步所導致的。

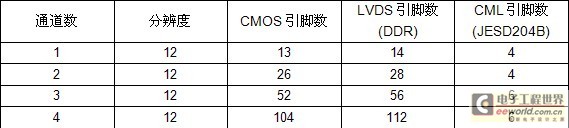

表1顯示,當12位轉換器以200 MSPS采樣速率運行時,JESD204B使用的CML(電流模式邏輯)輸出驅動器的功耗效率更具優勢。 由于數據的串行化,與LVDS和CMOS驅動器相比,給定分辨率下CML所需的輸出對數較少。 表中數據假設CMOS和LVDS輸出的每個通道均采用同步時鐘,使用CML輸出時JESD204B的最大數據速率為4.0 GB(比JESD204B限值12.5 GB的一半還低)。 使用JESD204B時,引腳數量明顯減少。

表1

引腳數量比較 – 200MSPS轉換器

借此,對以2.0GSPS采樣速率運行的12位轉換器進行進一步的討論。 通過表2,我們能夠更加清楚地看到使用JESD204B的好處。 因為使用CMOS輸出與千兆采樣轉換器接口完全不可行,所以本例中我們將不考慮CMOS。 在這種情況下,我們將轉換器通道數量限制為四通道。 為確保數據速率處于當今市場上大多數FPGA的限值范圍內,每位需要兩對LVDS輸出。 如表中所示,由于采用JESD204B減少了輸出引腳的數量,所以明顯降低了輸出路由的復雜性。

表2

引腳數量比較 – 2.0GSPS轉換器

綜上所述,LVDS并不會被完全淘汰。 因為MSPS系列轉換器仍擁有較大的市場。但是,LVDS需注意的是,JESD204B的時代即將到來!

評論