一種CPCI總線結構微波接收機的設計方案

0 引言

微波接收機是一種重要的無線通信設備,隨著車載、機載、艦載等移動環境下的應用需求的產生,微波接收機的小型化、模塊化、通用化是當前必須解決的問題。

Compact PCI 簡稱CPCI,是目前科研和軍工領域廣泛應用的一種工業計算機總線標準。CPCI 結合了PCI 總線的電氣、軟件標準和歐式卡的工業組裝技術標準,與PCI 規范完全兼容;定義了32 位數據總線 ( 可擴展到64 位),最高工作頻率為 33MHz ;能夠實現設備的即插即用;系統設計結構緊湊、可靠性高,適應各種運輸、使用環境。

結合CPCI 總線技術的微波接收機性能優良,可以滿足智能交通、航空航天等眾多領域的應用要求。

1 系統原理

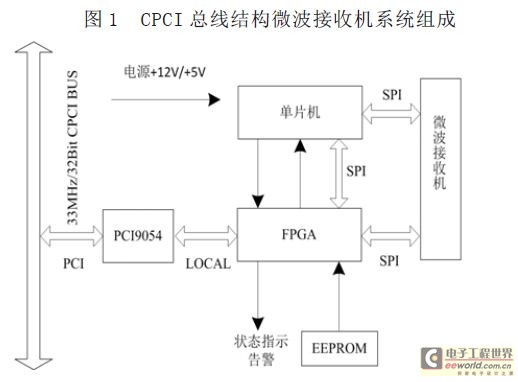

本接收機系統以FPGA 和單片機為中心控制單元,實現CPCI 總線結構下微波信號的接收、濾波、變頻、增益控制等功能。系統主要由微波接收機、PCI9054、FPGA(EP1C6Q240C8)和單片機(Atmega8L)組成,系統組成如圖1 所示。

CPCI 總線信號經高傳輸速率的PCI 橋芯片PCI9054 轉換為LOCAL Bus 信號,通過Verilog HDL 語言編程產生對FPGA 的控制信號,完成數據的快速讀寫,同時在外部采用EEPROM 進行高速數據的緩沖,從而實現與FPGA 與CPCI 總線的高速數據通信。在控制信號作用下,FPGA 實時接收LOCALBus 信號,并進行運算處理,對接收機增益進行控制;對系統鎖相環的控制指令、數據則通過串口發送給單片機,FPGA 和單片機共同完成對接收機系統的控制。系統供電由CPCI 機箱內5V、12V 開關電源提供。

2 關鍵技術設計

根據CPCI 總線規范及結構特點要求,CPCI 總線結構微波接收機系統的設計需要解決總線接口轉換、結構設計、電源設計以及電磁兼容設計等關鍵技術。

2.1 總線接口轉換

2.1.1 CPCI Bus 到LOCAL Bus 的接口設計

CPCI 總線信號到LOCAL 總線信號的轉換是基于PCI9054芯片實現的。PCI9054 是PLX 公司生產的一款基于PCI2.2總線規范的通用接口芯片,是32 位、33MHZ的PCI總線主I/O 加速器,突發傳輸速度可達132MB/s.有M、J、C 三種工作模式,本設計中選用數據線與地址線獨立使用的C 模式。

PCI9054 支持主控、目標、DMA( 直接存儲器訪問)3 種局部總線傳輸方式,這里采用了目標傳輸方式和高傳輸速率的DMA傳輸方式,即PCI9054 既是PCI 總線的目標,同時又是LOCAL總線的主控者。

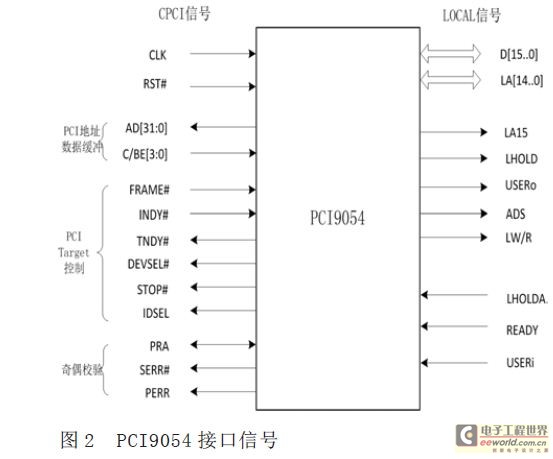

PCI9054 提供了3 種物理總線接口:CPCI 總線接口、LOCAL 總線接口和串行EEPROM 接口,其中需要用戶設計的是LOCAL 總線接口。其接口信號見圖2.

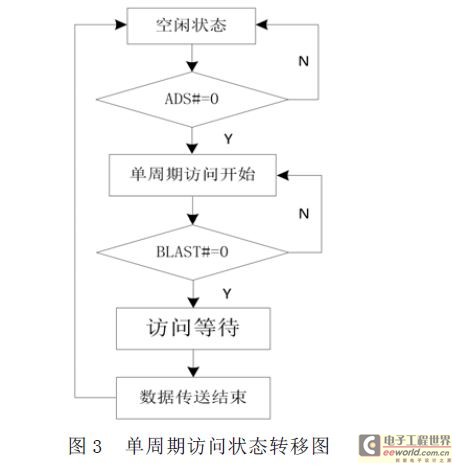

PCI9054 對本地設備的訪問有單周期訪問和突發方式訪問2 種訪問方式,單周期訪問可采用狀態機實現對LOCALBus 接口的控制,其狀態轉移如圖3 所示。

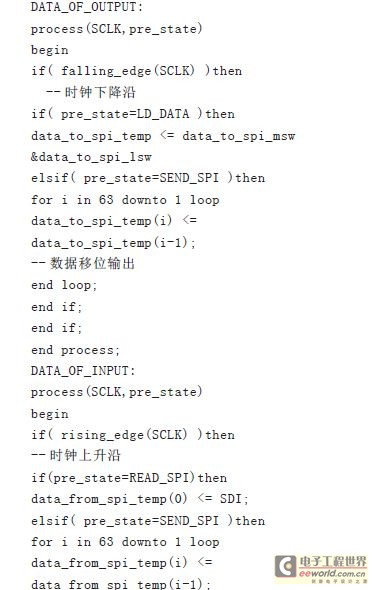

2.1.2 SPI 總線接口設計

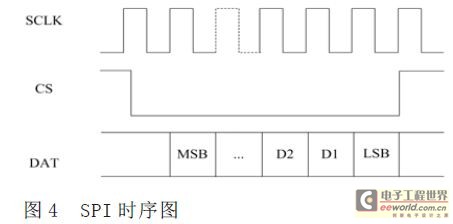

FPGA 與單片機的通信需要通過SPI 總線來實現。SPI總線是一種同步串行總線,以3 線或4 線方式通信。本設計中所使用的3 條通信線為:時鐘SCLK,數據DAT,片選信號CS.圖4 為SPI 工作時序。

當FPGA 從單片機讀取數據時,向單片機發送讀使能信號RD(可用任意I/O 口),串行數據經DAT 口在每個時鐘(SCK)的上升沿送入FPGA 的移位寄存器,全部接受完畢后,CS 置1 ;當FPGA 向單片機傳輸命令或者數據時,CS 拉低后,移位寄存器開始工作。內部并行數據經串/ 并轉換為64 位串行信號,每個時鐘的下降沿移位寄存器送出一位數據,單片機通過DAT 端口讀取數據。借助VHDL 硬件描述語言可方便地實現該系統,部分程序如下:

2.2 結構設計

微波接收機的全部硬件電路設計在一張CPCI 載板上,通過高密度2mm 插針式連接器安裝在一個6U 標準機箱內。機箱采用220V 交流供電,前面板設有狀態指示燈,可指示系統供電、PCI 總線訪問狀態及微波接收機內部射頻模塊鎖定狀態。

CPCI 總線結構的設計使該模塊具有“即插即用”的高度兼容性,方便接收機系統的建立、操作,且具有良好的抗震性,適合移動平臺的使用。

2.3 電源設計

由于CPCI 機箱提供的開關電源電磁干擾嚴重,且紋波系數較大,嚴重影響接收機雜散、相噪等性能,因此必須對電源進行處理。機箱內12V 開關電源經LM7809、LM7805、LT1965三級DC/DC 穩壓后,分別提供給系統中數字電路、模擬電路使用,有效降低了電源紋波和數字電路、模擬電路之間的電磁干擾。

2.4 電磁兼容設計

CPCI 結構微波接收機的電磁干擾來源有機箱內部的電源干擾及接收機的本振頻率泄露等。為了消除電源干擾的影響,將CPCI 機箱內計算機電源和接收機電源分開使用,并進行多級穩壓處理;模塊內敏感電路采用單獨的屏蔽盒進行隔離,減少頻率泄露;在PCB 板設計中將射頻線和控制線分層隔離;為了減小載板上其他模塊的信號對底板總線的影響,用10Ω的電阻在CPCI 卡的接插件J1 口處進行串聯電阻匹配。

3 實驗驗證

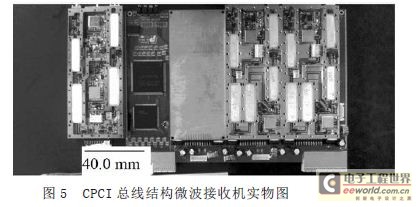

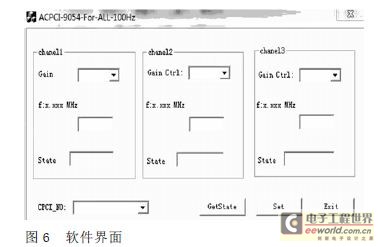

圖5 為按照本文設計方法完成的 CPCI 總線結構微波接收機實物。CPCI 載板上設有三個模塊,分別實現兩路中頻信號到S 頻段的上變頻和一路S 頻段信號到中頻的下變頻。中頻輸入、S 頻段輸出和參考信號輸入口均為SMA-50K.控制軟件能夠實現對上、下變頻器的增益控制和輸出、輸入頻率設置,以及每個變頻模塊鎖定狀態的讀取。其軟件控制界面如圖6 所示。

經過實際測試,本接收機軟、硬件設計滿足CPCI 總線結構微波接收機的控制及指標要求,通過驗證。

4 結束語

以CPCI 總線的工控機為平臺,結合6U 的CPCI 卡研制的微波接收機系統,將微波接收機技術與先進的計算機技術融為一體,解決了業界長期面臨的多通道、小型化、模塊化、PCI協議控制等射頻接收前端技術難題,具有廣闊的應用前景。

評論