JESD204B接口適合所有的應用嗎?

如果您有接觸使用 FPGA 的高速數據采集設計,沒準聽說過新術語“JESD204B”。

我在工作中看到過很多工程師詢問有關 JESD204B 接口的信息以及它如何同 FPGA 協作。他們特別感興趣的是 JESD204B 接口將如何簡化設計流程。

與LVDS 及CMOS 接口相比,JESD204B 數據轉換器串行接口標準可提供一些顯著的優勢,包括更簡單的布局以及更少的引腳數。因此它能獲得工程師的青睞和關注也就不足為奇了,它具備如下系統級優勢:

● 更小的封裝尺寸與更低的封裝成本:JESD204B 不僅采用 8b10b 編碼技術串行打包數據,而且還有助于支持高達 12.5Gbps 的數據速率。這可顯著減少數據轉換器和 FPGA 上所需的引腳數,從而可幫助縮小封裝尺寸,降低封裝成本;

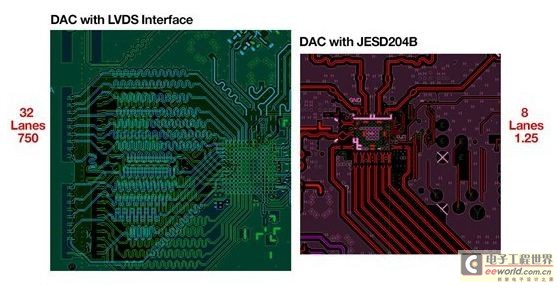

● 簡化的 PCB 布局與布線:更少的引腳數可顯著簡化 PCB 布局與布線,因為電路板上的路徑更少。由于對畸變管理的需求降低,因此布局和布線可進一步簡化。這是因為數據時鐘嵌入在數據流中,并在接收器中與彈性緩沖器結合,無需通過“波形曲線”來匹配長度。圖 1 是 JESD204B 接口對簡化 PCB 布局有多大幫助的實例;

● 高靈活布局:JESD204B 對畸變要求低,可實現更遠的傳輸距離。這有助于將邏輯器件部署在距離數據轉換器更遠的位置,以避免對靈敏模擬器件產生影響;

● 滿足未來需求:該接口能夠自適應不同數據轉換器分辨率。對于未來模數轉換器 (ADC) 及數模轉換器 (DAC) 而言,無需對 TX/RX 電路板進行物理上的重新設計。

圖 1:LVDS DAC 的 PCB 布局(左);采用 JESD204B 的相同 DAC 的 PCB 布局(右)

這是不是意味著您要改用 JESD204B 接口?

不一定。與 LVDS 接口相比,JESD204B 的缺點是具有更長的絕對時延,這對于有些應用來說是不可接受的。

盡管 JESD204B 可提供很多優勢,但有些應用要求極短的時延,最好是無時延。一個很好的實例是電子戰中使用的信號屏蔽器。該設備不僅要求絕對時延,而且需要最大限度地降低任何可能的延遲。

對于這種應用,您應該考慮 LVDS 接口,因此它沒有在 JESD204B 上進行數據串行化的延遲。

評論