基于FPGA的1553B總線接口設計

MIL-STD-1553總線是美國20世紀80年代制定的第一個軍用數據總線標準,它是一種串行的數據總線。該總線標準自制定后廣泛應用于軍用飛機、車輛、船舶中,并鑒于其高可靠性和靈活性,逐漸應用在許多其他機動平臺上。

1553B是一種時分制指令/響應式多路傳輸數據總線,總線上的所有消息傳輸都由總線控制器發起,遠程終端對發出的指令應給予回答(響應)并執行相關操作。這種方式非常適合集中控制的分布式處理系統。1553B總線通信系統是由總線控制器、遠程終端、總線監控器三部分組成。一個通信總線上最多可以掛32個遠程終端,傳輸介質采用屏蔽雙絞線,對噪聲等干擾有很好的抑制能力。1553B總線的數據傳輸率為1Mb/s,在一次消息傳輸中最多可以傳送32個字,所有單次傳輸的時間較短,具有很好的實時性。

在MIL-STD-1553總線通信系統中,總線接口板是系統的關鍵部分,其中核心部分的接口電路是總線應用中的主要制約因素。在1553B總線得到廣泛應用的今天,國內應用1553B總線協議的通信模塊的解決方案多采取基于進口1553B總線協議芯片來開展相關設計,如UT公司的UTl553B協議芯片、DDC公司的高級協議處理芯片BU-61580等,雖然這些芯片能夠完成協議功能,但價格昂貴、靈活性差,這些弱點在一定程度上限制了設計能力,因此提出一種新的基于嵌入式方法實現的1553B數據總線接口邏輯。

1 系統總體設計方案

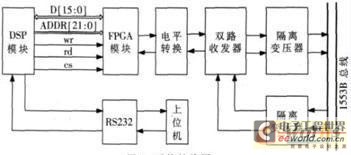

本文采用Xilinx公司的FPGA芯片作為協議處理核心器件,選用TI公司的TMS320C5510作為主處理器負責接收FPGA處理過的數據和調度FPGA的具體操作。總體方案的系統結構如圖1所示。

圖1 系統結構圖

1.1 模擬收發部分電路設計

由于1553B總線上傳輸的是雙極性的差分信號,主處理器不能直接接收來自總線上的數據,所以需要信號調制解調及電平轉換電路。

電平轉換部分一方面將總線上傳輸的電平信號轉換成標準的CMOS電平供處理器使用,另一方面將處理器發出的CMOS信號變成總線標準進行傳輸。模擬收發器部分簡單地說就是將單極性曼徹斯特編碼和雙極性曼徹斯特編碼相互轉換。本文采用HOLT公司的HI -1567PSI,它是一款專門為MIL-STD-1553開發的模擬收發器,供電電壓為3.3V,通過隔離變壓器連接到總線上。HI-1567PSI是雙通道收發器結構,因此要有兩個隔離變壓器與其相連接。

1.2 總線接口的數字通信部分

數字通信部分是1553B總線接口模塊的核心,完成協議數據的收發處理,由可編程邏輯器件Virtex系列芯片和DSP芯片組成。FPGA芯片在模塊中起到1553B通道的作用,接收總線上送來的數據并根據協議進行處理之后送給處理器。FPGA模塊中開辟了足夠空間的FIFO存儲處理后的數據,當達到一定數量后,主處理器采用中斷的方式讀取FIFO中的數據。在本文的設計中,為了便于觀察實驗結果,將DSP接收到的數據送到串口上進行顯示。同樣地,DSP將要發送的數據送到FPGA開辟的另一個FIFO中,當每個數據編碼結束后通過狀態機程序產生FIFO信號的時鐘讀取下一個數據進行編碼,所以這里的FIFO采用的是異步的工作方式。

2 核心模塊功能分析

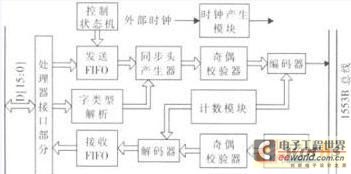

總線接口模塊最主要的部分是FPGA實現的功能,其總體功能如圖2所示。

圖2 FPGA功能圖

FPGA中最重要的部分是發送器和接收器,現將這兩部分的工作過程做簡要分析。

評論