DS90CF364 LVDS發送/接收器在RGB液晶屏應用

3.2引腳功能本文引用地址:http://www.104case.com/article/201612/331356.htm

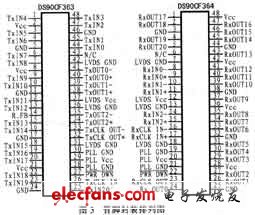

圖3給出了DS90C363和DS90CF364的引腳排列,其中發送器DS90C363的引腳功能如下:

TxIN0~TxIN20:TEL電乎數據輸入,其中包括6紅、6綠、6藍以及3個控制線-FPLINE(HSYNC)、FPFRAME(VSYNC)和DRDY(Data Enable);

TxOUT+:LVDS差分數據輸出的正端;

TxOUT-:LVDS差分數據輸出的負端;

TxCLK IN:TIL電平時鐘輸入,一般在其下降沿激活數據。

R_FB:可編程觸發選通;

TxCLK OUT+:LVDS差分時鐘輸出正端;

TxCLK OUT-:LVDS差分時鐘輸出負端;

PWR DWN:TTL電平輸入,當設置為低時為三態,以確保在節能狀態的低電流;

Vcc:用于TTL的電源引腳;

GND:用于TTL的電源地;

PLL Vcc:用于PLL,的電源引腳;

PLL GND:用于PLL的電源地;

LVDS Vcc:用于LVDS輸出的電源引腳;

LVDS GND:用于LVDS輸出的電源地。

接收器DS90CF364引腳功能如下:

RxOUT0~RxOUT20:TTL電平數據輸出,包括6紅、6綠、6藍以及3個控制線-FPLINE(HSYNC)、FPFRAME(VSYNC)和DRDY(Data Enable)。;

RxIN+:LVDS差分數據輸入的正端;

RxIN-:LVDS差分數據輸入的負端;

RxCLK OUT:TTL電平時鐘輸出,通常在其下降沿激活數據;

RxCLK IN+:LVDS差分時鐘輸入正端;

RxCLK IN-:LVDS差分時鐘輸入負端;

PWR DWN:TTL電平輸入,當設置為低時,輸出為三態,以便確保在節能狀態下的低電流;

Vcc:用于TTL的電源引腳;

GND:用于TTL的電源地;

PLL Vcc:用于PLL的電源引腳;

PLL GND:用于PLL的電源地;

LVDS Vcc:用于LVDS輸出的電源引腳;

LVDS GND:用于LVDS輸出的電源地。

4 設計應用

本文所介紹的系統板設計并不是太難,但需注意以下兩點:

(1)PCB板設計

最好使用4層板,從頂層到底層的順序依次為LVDS信號層、地層、電源層、TFL信號層,這樣可使TIL信號和LVDS信號相互隔離,否則T1L可能會耦合到LVDS線上,鑒于上述原因,設計時最好將TIL和LVDS信號放在由電源/地層隔離的不同層上。安裝時,LVDS發送器和接收器應盡可能地靠近連接器的LVDS端。使用分布式的多個電容來旁路LVDS設備時,表面貼電容應盡量靠近電源/地層管腳放置,以進行更好地濾波和防止電源干擾。電源層和地層應盡量布一些粗線,以保持PCB地線層返回路徑寬且短,應該利用地層返回銅線的電纜連接兩個系統的地層,可使用多過孔(至少兩個)將其連接到電源層(線)和地層(線),表面貼電容可以直接焊接到過孔焊盤以減少線頭。所有未使用的LVDS接收器輸入管腳均應懸空,同時所有未使用的LVDS和TIL輸出腳也應懸空,并將未使用的TIL發送/驅動器輸入和控制/使能管腳接到電源或地端。

(2)電纜選擇

使用受控阻抗媒質時,其差分阻抗約為100Ω,因而不會引入較大的阻抗不連續性,但就減少噪聲和提高信號質量而言,平衡電纜(如雙絞線對)通常比非平衡電纜好。電纜長度小于0.5m時,大部分電纜都能有效工作,距離在0.5-10m之間時,CAT 3(Categiory 3)雙絞線對電纜的效果較好,因此,在距離大于10m并且要求高速率時,建議使用CAT 5雙絞線對。如需在噪聲環境中提高可靠性,最好選用帶屏蔽層的電纜,每對電纜之間一定要靠緊,并且應在盡量靠近接收器的每對平行線正端和負端之間連接一個100Ω的表面貼終端電阻,該電阻可在設計時起到終止環流信號的作用。另外在接收端串接一個變壓器可以減小干擾并避免LVDS驅動器和接收器地電位差所產生的影響。

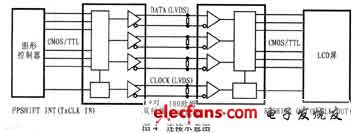

該芯片組的應用連接示意圖如圖4所示,設計時可參照該圖進行。

5 結束語

本文介紹的LVDS傳輸套片還可運用于其它具有數字RGB視頻接口的控制芯片。對于美國國家半導體公司出品的其它FPD鏈路專用LVDS傳輸套片,也可借鑒本文所介紹的方法來進行設計和調試。

評論