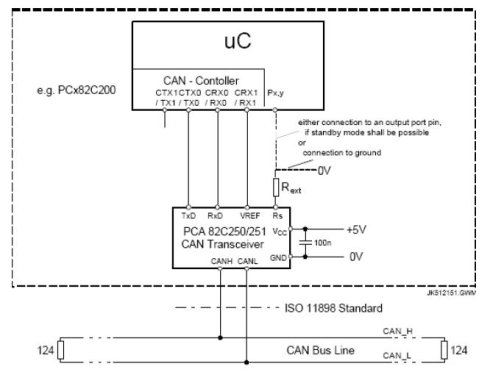

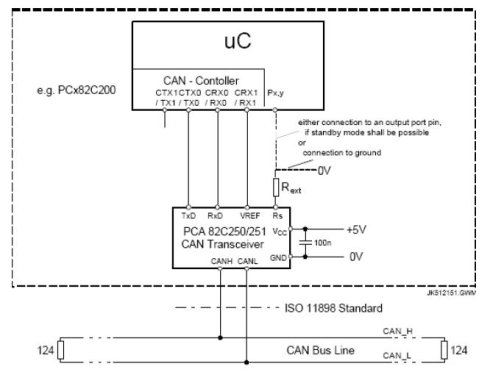

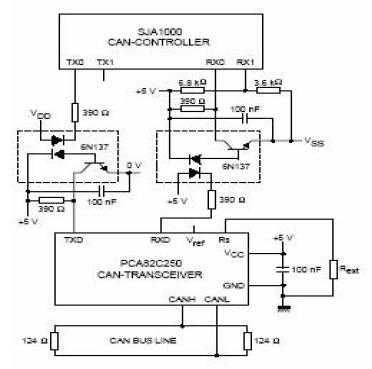

圖2-7 PCA82C250/251 收發器的應用舉例

應用舉例

PCA82C250/251 收發器的典型應用如圖2-7所示協議控制器通過串行數據輸出線TX 和串行數據輸入線RX 連接到收發器收發器通過有差動發送和接收功能的兩個總線終端CANH 和CANL 連接到總線電纜輸入Rs 用于模式控制參考電壓輸出VREF的輸出電壓是額定VCC 的0.5倍其中收發器的額定電源電壓是5V。

協議控制器輸出一個串行的發送數據流到收發器的TxD 引腳內部的上拉功能將TxD 輸入設置成邏輯高電平也就是說總線輸出驅動器默認是被動的在隱性狀態中見圖2-7CANH 和CANL 輸入通過典型內部阻抗是17k 的接收器輸入網絡偏置到2.5V 的額定電壓另外如果TxD 是邏輯低電平總線的輸出級將被激活在總線電纜上產生一個顯性的信號電平。輸出驅動器由一個源輸出級和一個下拉輸出級組成CANH 連接到源輸出級CANL 連接到下拉輸出級在顯性狀態中CAN_H 的額定電壓是3.5V CAN_L是1.5V。

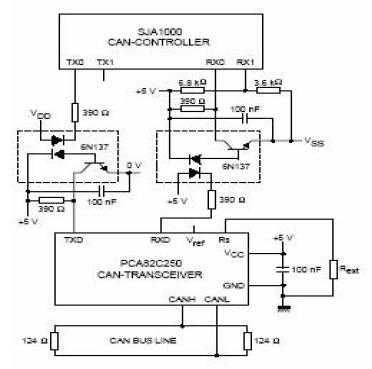

2.2.3.2基于82C250收發電路設計

82C250是CAN控制器與物理總線間的接口,可以提供對總線的差動發送和接收能力,與IS011898標準完全兼容,并具有抗汽車環境下的瞬間干擾、保護總線的能力。

設計中,收發器的接受、發送腳原理上要和SJA1000的發送、接受腳相連接。但這樣一來,兩者的電氣不一致,造成電氣隔離,給通信帶來麻煩。為此,在它們之間接上高速光耦合器6N137,避開了電氣隔離,更好的實現通信聯系。82C250的TXD、RXT就對應接上6N137的輸出腳OUT和輸入腳IN;腳Rs作為斜率控制電阻輸入端,電阻的大小可以割據總線通信速度適當調整一般在16~140KΩ之間,設計中Rs阻值為47KΩ。在通過接一個47K電阻分流之后,可以接地。電壓引腳Vcc,其電源電壓:4.5V〈 Vcc〈 5.5V,在設計中采用5V電壓。Vref作為基準電壓輸出端,設計中可以接地。而CANH,CANL腳是信號的輸入輸出,實現對電平信號的傳送,通過它們連接上雙絞線,完成通信傳輸。電路大致如下

圖2-8 82C250收發電路

2.2.4復位、監控電路設計

2.2.4.1X5045P簡介

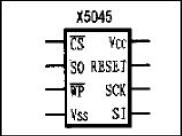

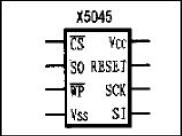

本設計中,所應用到的復位電路采用Xicor公司產品X5045P。X5045P把四種常用的功能:上電復位、看門狗定時器、電源電壓監控和塊鎖(Block Lock TM )保護的串行EEPROM存儲器組成在一個封裝之內。這種組合降低了系統成本、減少了電路板空間和增加了可靠性。下圖2-9為引腳圖:

圖2-9 X5045P引腳配置

CS/WDI:片選輸入/看門狗復位輸入;

SO:串行輸出;

WP:寫保護輸入;

Vss:地;

Vcc:電源;

RESET:復位輸出; 15

SCK:同步時鐘輸入;

SI:串行輸入。

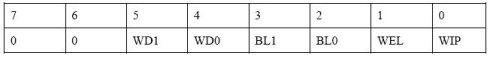

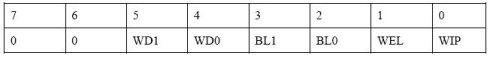

X5045P的狀態寄存器描述器件的當前狀態,各位意義如表5所列。

表5 X5045P狀態寄存器

其中,WD1、WD0是看門狗定時時間設置位;BL1、BL0是存儲單元寫保護區設置位;WEL是只讀標志,1表明寫使能開關打開;WIP也是只讀標志,1代表芯片內部正處于寫周期。電復位時,各位都被清零。

X5045P芯片功能包括以下4種:

(1)上電復位控制。在對X5045P通電時,ERSET引腳輸出有效的復位信號,并保持至少200ms,使CPU有效復位。

(2)電源電壓監控。當檢測到電源電壓低于內部門檻電壓VTRIP時,RESET輸出復位信號,直至電源電壓高于VTRIP并保持至少200ms,復位信號才被撤消。VTRIP的出廠值根據芯片型號不同共有5個級別的電壓范圍。對于需要電源電壓精確監控的應用,用戶可以搭建編程電路,對芯片內VTRIP電壓進行微調。

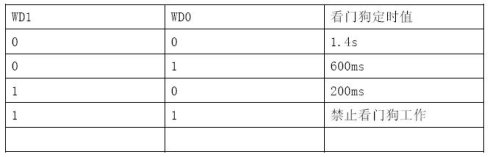

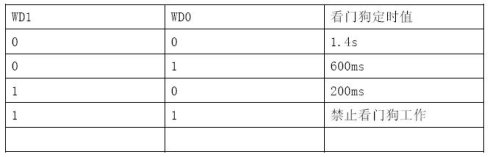

(3)看門狗定時器。芯片內部狀態寄存器的WD1、WD0是看門狗定時設置位,通過狀態寄存器寫指令WRSR修改這2個標志位,就能在3種定時間隔中進行選擇或關閉定時器。對看門狗的復位由CS輸入電平的下降沿完成。表6是WD1、WD0組合的含義

表6 內部寄存器WD1、WD0含義

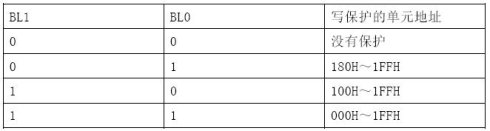

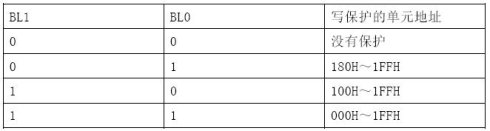

(4)串行E2PROM。芯片內含512字節存儲單元,10萬次可靠寫,數據保持時間100年。XICOR設計了3種保護方式防止誤寫。包括:WP寫保護引腳,當引腳被拉低時,內部存儲單元狀態寄存器都禁止寫入;存儲區域寫保護模式,通過對狀態寄存器的BL1、BL0位的設置,可以選擇對不同的存儲區域進行寫保護;在進行任何寫操作前都必須打開寫使能開關,而且在上電初始化寫操作完成時,寫使能開關自動關閉。顯然,在幾方面的保護之下,產生誤寫的可能性極小,表7是BL1、BL0組合的含義。

表7串行E2PROM的BL1、BL0含義

對X5045P的操作是通過4根口線CS、SCK、SI和SO進行同步串行通信來完成的。SCK是外部輸入的同步時鐘信號。在對芯片定改指令或數據時,時鐘前沿將SI引腳信號輸入;在讀郵數據時,時鐘后沿將數據位輸出到SO引腳上。數據的輸入/輸出都是高位在先。

芯片內部共有6條指令,如表8所列。

表8 X5045P內部指令

(1)WREN和WRDI是寫使能開關的開/關指令。它們都是單字節指令。

(2)RDSR和WRSR是狀態寄存器的讀/寫指令。在從SI輸入指令后,RDSR的執行結果,即狀態寄存器內容須從SO讀出;而WRSR需要緊接著輸入修改數據。

(3)READ和WEITE是存儲單元的讀/寫指令。輸入指令后(指令碼第三代表存儲單元地址的最高位),接著輸入低八位地址,最后就可以連續讀出或寫入數據。其中,讀指針和寫指針的工作方式完全不同,讀指針的全部8位用來計數,0FFH溢出后變成00H;寫指針只用最低兩位計數,XXXXXX11B溢出后變成XXXX XX00B,所以連續寫的實際結果是在4個單元中反復寫入。另外,由于E2PROM的寫入時間長,所以在連續兩條寫指令之間應讀取WIP狀態,只有內部寫周期結束時才可輸入下一條寫指令。

X5045P中的看門狗對系統提供了保護功能。當系統發生故障而超過設置時間時,電路中的看門狗將通過RESET信號向CPU 作出反應。X5045提供了三個時間值供用戶選擇使用。它所具有的電壓監控功能還可以保護系統免受低電壓的影響,當電源電壓降到允許范圍以下時,系統將復位,直到電源電壓返回到穩定值為止。X5045P的存儲器與CPU 可通過串行通信方式接口,共有4096個位,可以按512 x 8個字節來放置數據。

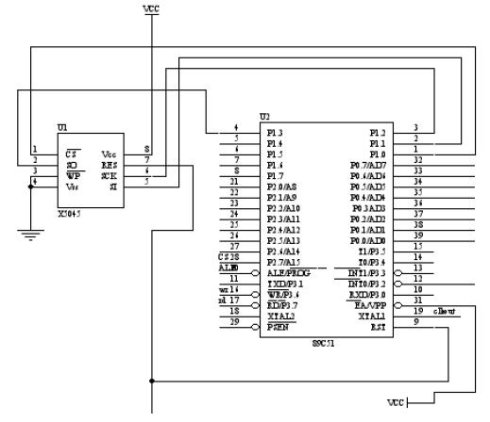

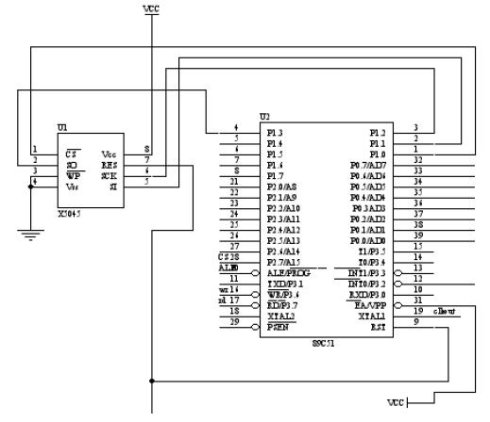

2.2.4.2基于X5045P的電路設計

X5045P在本設計中做為復位、監控電路使用,雖然增加了電路連接的復雜和成本,但對于電路的穩定和可靠性有起到很大的作用,是系統中不可缺少的部分。

對X5045的操作是通過4根口線CS、SCK、SI和SO進行同步串行通信來完成的。SCK是外部輸入的同步時鐘信號。在對芯片定改指令或數據時,時鐘前沿將SI引腳信號輸入;在讀郵數據時,時鐘后沿將數據位輸出到SO引腳上。數據的輸入/輸出都是高位在先。在設計中,/CS腳和單片機P1.0、SI、SCK、SO、RST分別與單片機的引腳P1.0~P1.3、RST連接。對于不用到的引腳,可以直接和地相連。電路設計如下:

圖2-10 X5045P電路監控、復位電路

評論