I2S總線協(xié)議

音響數(shù)據(jù)的采集、處理和傳輸是多媒體技術(shù)的重要組成部分。眾多的數(shù)字音頻系統(tǒng)已經(jīng)進入消費市場,例如數(shù)字音頻錄音帶、數(shù)字聲音處理器。對于設(shè)備和生產(chǎn)廠家來說,標準化的信息傳輸結(jié)構(gòu)可以提高系統(tǒng)的適應(yīng)性。I2S(Inter—IC Sound)總線是飛利浦公司為數(shù)字音頻設(shè)備之間的音頻數(shù)據(jù)傳輸而制定的一種總線標準,該總線專責于音頻設(shè)備之間的數(shù)據(jù)傳輸,廣泛應(yīng)用于各種多媒體系統(tǒng)。它采用了沿獨立的導(dǎo)線傳輸時鐘與數(shù)據(jù)信號的設(shè)計,通過將數(shù)據(jù)和時鐘信號分離,避免了因時差誘發(fā)的失真,為用戶節(jié)省了購買抵抗音頻抖動的專業(yè)設(shè)備的費用。

I2S有3個主要信號

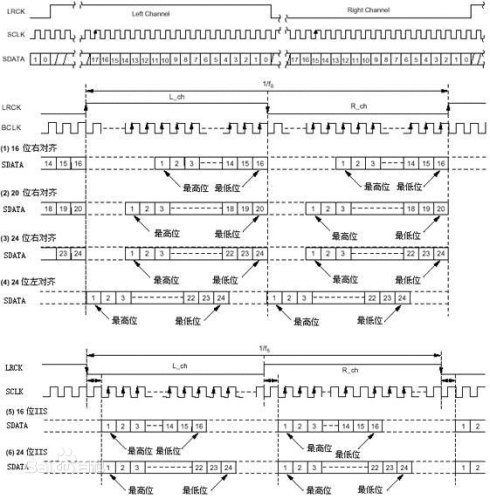

1.串行時鐘SCLK,也叫位時鐘(BCLK),即對應(yīng)數(shù)字音頻的每一位數(shù)據(jù),SCLK都有1個脈沖。SCLK的頻率=2×采樣頻率×采樣位數(shù)。

串行數(shù)據(jù)(SD)

I2S格式的信號無論有多少位有效數(shù)據(jù),數(shù)據(jù)的最高位總是出現(xiàn)在LRCK變化(也就是一幀開始)后的第2個SCLK脈沖處。這就使得接收端與發(fā)送端的有效位數(shù)可以不同。如果接收端能處理的有效位數(shù)少于發(fā)送端,可以放棄數(shù)據(jù)幀中多余的低位數(shù)據(jù);如果接收端能處理的有效位數(shù)多于發(fā)送端,可以自行補足剩余的位。這種同步機制使得數(shù)字音頻設(shè)備的互連更加方便,而且不會造成數(shù)據(jù)錯位。

隨著技術(shù)的發(fā)展,在統(tǒng)一的

為了保證數(shù)字音頻信號的正確傳輸,發(fā)送端和接收端應(yīng)該采用相同的數(shù)據(jù)格式和長度。當然,對I2S格式來說數(shù)據(jù)長度可以不同。

字段(聲道)選擇(WS)命令選擇線表明了正在被傳輸?shù)穆暤?/p>

WS=1,表示正在傳輸?shù)氖怯衣暤赖臄?shù)據(jù)。

WS=0,表示正在傳輸?shù)氖亲舐暤赖臄?shù)據(jù)。

WS可以在串行時鐘的上升沿或者下降沿發(fā)生改變,并且WS信號不需要一定是對稱的。在從屬裝置端,WS在時鐘信號的上升沿發(fā)生改變。WS總是在最高位傳輸前的一個時鐘周期發(fā)生改變,這樣可以使從屬裝置得到與被傳輸?shù)拇袛?shù)據(jù)同步的時間,并且使接收端存儲當前的命令以及為下次的命令清除空間。

輸出電壓:VL <0.4V,VH>2.4V

輸入電壓:VIL=0.8V,VIH=2.0V

注:這是使用的TTL電平標準,隨著其他IC(LSI)的流行,其他電平也會支持。

時序要求

在I2s總線中,任何設(shè)備都可以通過提供必需的時鐘信號成為系統(tǒng)的主導(dǎo)裝置,而從屬裝置通過外部時鐘信號來得到它的內(nèi)部時鐘信號,這就意味著必須重視主導(dǎo)裝置和數(shù)據(jù)以及命令選擇信號之間的傳播延遲,總的延遲主要由兩部分組成:

1.外部時鐘和從屬裝置的內(nèi)部時鐘之間的延遲

2.內(nèi)部時鐘和數(shù)據(jù)信號以及命令選擇信號之間的延遲

對于數(shù)據(jù)和命令信號的輸入,外部時鐘和內(nèi)部時鐘的延遲不占據(jù)主導(dǎo)地位,它只是延長了有效的建立時間(set—up time)。延遲的主要部分是發(fā)送端的傳輸延遲和設(shè)置接收端所需的時間。T是時鐘周期,Tr是最小允許時鐘周期,T>Tr這樣發(fā)送端和接收端才能滿足數(shù)據(jù)傳輸速率的要求。對于所有的數(shù)據(jù)速率,發(fā)送端和接收端均發(fā)出一個具有固定的傳號空號比(mark—space ratio)的時鐘信號,所以t LC和tHC是由T所定義的。

評論