片上總線Wishbone 學(xué)習(xí)(十二)總線周期之RMW操作

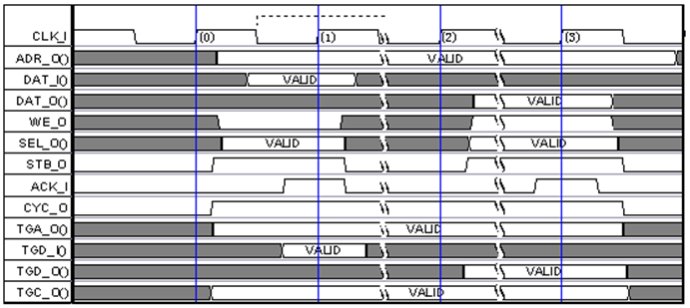

一次RMW操作對于總線來說,本質(zhì)上是兩次子操作,一次讀,一次寫,只不過這兩次子操作必須由同一個主設(shè)備的完成,且讀數(shù)據(jù)和寫數(shù)據(jù)的地址相同。"改"是不發(fā)生在總線上的,它發(fā)生在主設(shè)備內(nèi)部。一個RMW操作的例子如圖13所示,其過程如下:

在時鐘上升沿0,主設(shè)備將地址信號ADR_O()、TGA_O()放到總線上,將WE_O置為低表示讀操作,將適當(dāng)?shù)腟EL_O()信號置高通知從設(shè)備將數(shù)據(jù)放在數(shù)據(jù)總線的適當(dāng)位置,將CYC_O和TGC_O()置高表示操作正在進(jìn)行,將STB_O置高表示第一次子操作開始。CYC_O和TGC_O()可以發(fā)生在上升沿0以前的任何時刻。

在時鐘上升沿1到達(dá)之前,從設(shè)備檢測到主設(shè)備發(fā)起的操作,將適當(dāng)?shù)臄?shù)據(jù)放到主設(shè)備的DAT_I()和TGD_I(),將主設(shè)備的ACK_I置高作為對主設(shè)備STB_O的響應(yīng)。

在時鐘上升沿1,主設(shè)備發(fā)現(xiàn)ACK_I信號為高,將DAT_I()和TGD_I()采樣,完成第一次子操作。主設(shè)備將STB_O置低表示插入等待。

在時鐘上升沿1之后新的上升沿到達(dá)之前,從設(shè)備檢測到主設(shè)備將STB_O置低,于是將ACK_I置低。

經(jīng)過若干等待周期,在上升沿2,主設(shè)備將地址信號ADR_O()、TGA_O()放到總線上,將數(shù)據(jù)信號DAT_O()、TGD_O()放到總線上,將WE_O置為高表示寫操作,將適當(dāng)?shù)腟EL_O()信號置高通知從設(shè)備將數(shù)據(jù)總線上哪些信號是有效的,將STB_O置高表示第二次子操作開始。

在時鐘上升沿3到達(dá)之前,從設(shè)備檢測到主設(shè)備發(fā)起的操作,將主設(shè)備的ACK_I置高作為對主設(shè)備STB_O的響應(yīng)。

在時鐘上升沿3,從設(shè)備將DAT_I()和TGD_I()采樣;主設(shè)備發(fā)現(xiàn)ACK_I信號為高,得知第二次子操作完成,于是將STB_O和CYC_O置低表示整個RMW操作完成。

在時鐘上升沿之后,從設(shè)備發(fā)現(xiàn)STB_O為低,于是將ACK_I置低。

圖 Wishbone總線的RMW操作

評論