IIC總線協(xié)議

處理器和芯片間的通信可以形象的比喻成兩個人講話:1、你說的別人得能聽懂:雙方約定信號的協(xié)議。2、你的語速別人得能接受:雙方滿足時序要求。

本文引用地址:http://www.104case.com/article/201612/329864.htm看IIC協(xié)議先:兩條線可以掛多個設備。IIC設備(稍微有點智能的)里有個固化的地址。只有在兩條線上傳輸?shù)闹档扔谖遥↖IC設備)的地址時,我才作出響應。

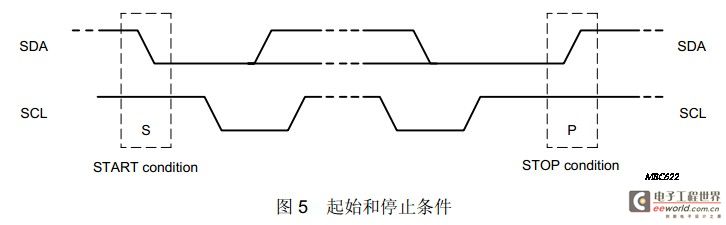

開始信號:處理器讓SCL時鐘保持高電平,然后讓SDA數(shù)據(jù)信號由高變低就表示一個開始信號。同時IIC總線上的設備檢測到這個開始信號它就知道處理器要發(fā)送數(shù)據(jù)了。

停止信號:處理器讓SCL時鐘保持高電平,然后讓SDA數(shù)據(jù)信號由低變高就表示一個停止信號。同時IIC總線上的設備檢測到這個停止信號它就知道處理器已經(jīng)結束了數(shù)據(jù)傳輸,我們就可以各忙各個的了,如休眠等。

再看數(shù)據(jù)怎么傳:SDA上傳輸?shù)臄?shù)據(jù)必須在SCL為高電平期間保持穩(wěn)定:因為外接IIC設備在SCL為高電平的期間采集數(shù)據(jù)方知SDA是高或低電平。SDA上的數(shù)據(jù)只能在SCL為低電平期間翻轉變化。

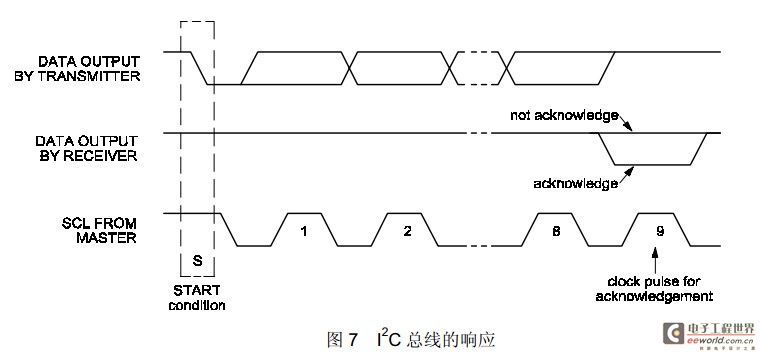

響應信號(ACK):處理器把數(shù)據(jù)發(fā)給外接IIC設備,如何知道IIC設備數(shù)據(jù)已經(jīng)收到呢?就需要外接IIC設備回應一個信號給處理器。處理器發(fā)完8bit數(shù)據(jù)后就不再驅動總線了(SDA引腳變輸入),而SDA和SDL硬件設計時都有上拉電阻,所以這時候SDA變成高電平。那么在第8個數(shù)據(jù)位,如果外接IIC設備能收到信號的話接著在第9個周期把SDA拉低,那么處理器檢測到SDA拉低就能知道外接IIC設備數(shù)據(jù)已經(jīng)收到。

IIC數(shù)據(jù)從最高位開始傳輸。

再進一步說:IIC總線是允許掛載多個設備的,如何訪問其中一個設備而不影響其他設備呢?

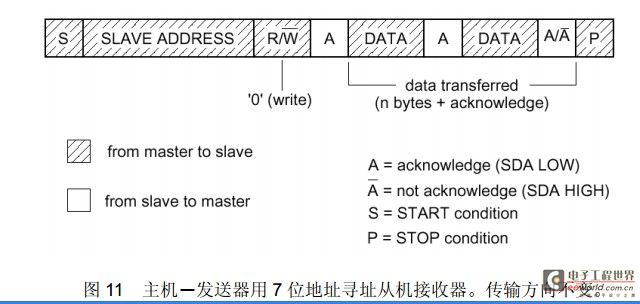

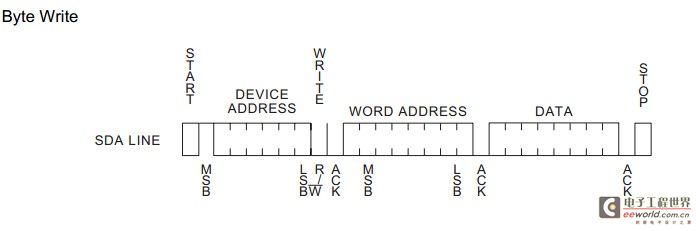

用7bit表示從地址,那么可以掛載的從設備數(shù)是2的7次方128個。處理器想寫的話:先發(fā)送起始位,再發(fā)一個8bit數(shù)據(jù):前7bit表示從地址,第8bit表示讀或者寫。0write是處理器往IIC從設備發(fā),1read是IIC從設備往處理器發(fā)。第9個時鐘周期回復響應信號。

下面就以AT24Cxx為例詳細說明一下:

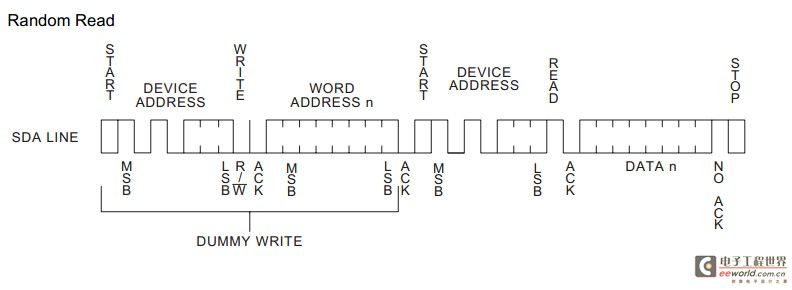

首先發(fā)出一個start信號,從設備地址,R/W(0,寫),回應ACK表示有這個從設備存在。這時候是處理器從指定的從設備讀數(shù)據(jù)的從設備里8bit存儲地址的指定。所以這里R/W是0為寫。ACK回應有這個設備的話,處理器把要訪問的從設備里的8bit存儲地址寫好。ACK對方回應。繼續(xù)一個start信號+從設備地址,最低位是高電平表示讀數(shù)據(jù),回應ACK表示有這個從設備存在。在讀數(shù)據(jù)的時候,每發(fā)出一個時鐘,處理器會SDA上的數(shù)據(jù)存起來。那么發(fā)出8個時鐘后處理器就能得到8位的數(shù)據(jù)。這時候若想連續(xù)讀就不斷回應ACK信號否則就發(fā)出停止信號。

讀的過程:start信號,從設備地址,寫,待讀取存儲地址,再一個start信號,從設備地址,讀,8個時鐘,從設備就把對應的數(shù)據(jù)反饋給處理器。

start信號,哪一個設備地址,寫,緊跟連續(xù)兩個字節(jié)的數(shù)據(jù):要寫的地址,對方收到8bit地址后回應ACK,再8bit數(shù)據(jù)發(fā)給從設備,對方收到8bit數(shù)據(jù)后回應ACK,處理器寫完后發(fā)送停止信號。

評論