AXI總線學習

AXI 有讀地址和控制、讀數據、寫地址和控制、寫數據、寫響應5個通道。

控制和數據通道分離,可以帶來很多好處。地址和控制信息相對數據的相位獨立,可以先發地址,然后再是數據,這樣自然而然的支持顯著操作,也就是outstanding操作。Master訪問slave的時候,可以不等需要的操作完成,就發出下一個操作。這樣,可以讓slave在控制流的處理上流水起來,達到提速的作用。同時對于master,也許需要對不同的地址和slave就行訪問,所以可以對不同的slave 連續操作。而這樣的操作,由于slave返回數據的先后可能不按照master 發出控制的先后進行,導致出現了亂序操作(out of order )。

AXI的性能

AXI 能夠使SoC 以更小的面積、更低的功耗,獲得更加優異的性能。AXI獲得如此優異性能的一個主要原因,就是它的單向通道體系結構。單向通道體系結構使得片上的信息流只以單方向傳輸,減少了延時。

選擇采用何種總線,我們要評估到底怎樣的總線頻率才能滿足我們的需求,而同時不會消耗過多的功耗和片上面積。ARM一直致力于以最低的成本和功耗追求更高的性能。這一努力已經通過連續一代又一代處理器內核的發布得到了實現,每一代新的處理器內核都會引入新的流水線設計、新的指令集以及新的高速緩存結構。這促成了眾多創新移動產品的誕生,并且推動了ARM架構向性能、功耗以及成本之間的完美平衡發展。

AXI總線是一種多通道傳輸總線,將地址、讀數據、寫數據、握手信號在不同的通道中發送,不同的訪問之間順序可以打亂,用BUSID來表示各個訪問的歸屬。主設備在沒有得到返回數據的情況下可發出多個讀寫操作。讀回的數據順序可以被打亂,同時還支持非對齊數據訪問。

AXI總線還定義了在進出低功耗節電模式前后的握手協議。規定如何通知進入低功耗模式,何時關斷時鐘,何時開啟時鐘,如何退出低功耗模式。這使得所有IP在進行功耗控制的設計時,有據可依,容易集成在統一的系統中。

AXI的特點

單向通道體系結構。信息流只以單方向傳輸,簡化時鐘域間的橋接,減少門數量。當信號經過復雜的片上系統時,減少延時。

支持多項數據交換。通過并行執行猝發操作,極大地提高了數據吞吐能力,可在更短的時間內完成任務,在滿足高性能要求的同時,又減少了功耗。

獨立的地址和數據通道。地址和數據通道分開,能對每一個通道進行單獨優化,可以根據需要控制時序通道,將時鐘頻率提到最高,并將延時降到最低。

增強的靈活性。AXI技術擁有對稱的主從接口,無論在點對點或在多層系統中,都能十分方便地使用AXI技術。

AXI4的工作模式

握手機制

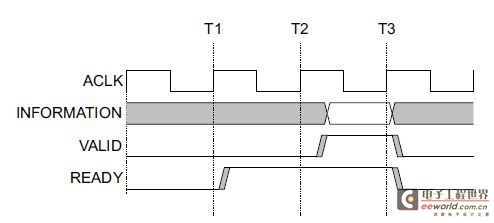

AXI4所采用的是一種READY,VALID握手通信機制,即主從模塊進行數據通信前,新根據操作對各所用到的數據、地址通道進行握手。主要操作包括傳輸發送者A等到傳輸接受者B的READY信號后,A將數據與VALID信號同時發送給B。如下圖所示:

axi總線的五個通道:

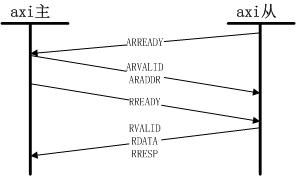

- 讀地址通道,包含ARVALID, ARADDR, ARREADY信號;

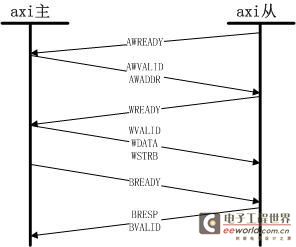

- 寫地址通道,包含AWVALID,AWADDR, AWREADY信號;

- 讀數據通道,包含RVALID, RDATA, RREADY, RRESP信號;

- 寫數據通道,包含WVALID, WDATA,WSTRB, WREADY信號;

- 寫應答通道,包含BVALID, BRESP, BREADY信號;

- 系統通道,包含:ACLK,ARESETN信號;

其中ACLK為axi總線時鐘,ARESETN是axi總線復位信號,低電平有效;讀寫數據與讀寫地址類信號寬度都為32bit;READY與VALID是對應的通道握手信號;WSTRB信號為1的bit對應WDATA有效數據字節,WSTRB寬度是32bit/8=4bit;BRESP與RRESP分別為寫回應信號,讀回應信號,寬度都為2bit,‘h0代表成功,其他為錯誤。

A.讀操作:

順序為主與從進行讀地址通道握手并傳輸地址內容,然后在讀數據通道握手并傳輸所讀內容以及讀取操作的回應,時鐘上升沿有效。如圖所示:

B.寫操作:

順序為主與從進行寫地址通道握手并傳輸地址內容,然后在寫數據通道握手并傳輸所讀內容,最后再寫回應通道握手,并傳輸寫回應數據,時鐘上升沿有效。如圖所示:

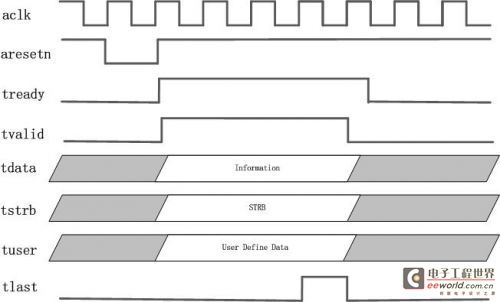

axis分為:

- tready信號:從告訴主做好傳輸準備;

- tvalid信號:主告訴從數據傳輸有效;

- tlast信號:主告訴從該次傳輸為突發傳輸結尾;

- tdata信號:數據,可選寬度32,64,128,256bit

- tstrb信號:為1的bit為對應tdata有效字節,寬度為tdata/8

- tuser信號 :用戶定義信號,寬度為128bit

- aclk信號:總線時鐘,上升沿有效;

- aresetn信號:總線復位,低電平有效;

通信時序如圖所示:

axi與axis是AXI4總線中通信復雜度較低的兩條總線,最大開發難度存在于axi的控制平面向axis的數據平面下發參數時,由于axi與axis時鐘頻率不同而產生的跨時鐘域數據傳輸問題。

AXI4:主要面向高性能地址映射通信的需求;

AXI4-Lite:是一個簡單地吞吐量地址映射性通信總線;

AXI4-Stream:面向高速流數據傳輸;

AXI4總線分為主、從兩端,兩者間可以連續的進行通信。

ISE從12.3版本,Virtex6,Spartan6芯片開始對AXI4總線提供支持,并且隨著Xilinx與ARM的合作面逐漸展開而得到大力推廣。

AXI4的優勢

1.通過統一的AXI接口,開發者為開發ip core只需要學習一種協議即可;

2.AXI4是面向地址映射的接口,允許最大256輪的數據突發傳輸;

3.AXI4-Lite是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元;

4.AXI4-Stream去掉了地址項,允許無限制的數據突發傳輸規模;

評論