I2C總線接口擴展技術

i2c總線(inter ic bus,又常寫作iic總線或i2c總線)是philips公司推出的新一代串行通信標準總線。它與spi、microwire/plus串行接口不同,僅僅依靠兩根連線實現了完善的全雙工同步數據傳送:一根為串行數據線(sda),一根為串行時鐘線(scl)。由于i2c總線具有接口電路簡單,可進行系統的模塊化、標準化設計,靈活性強,可維護性好等特性,目前已成為一種重要的串行通信總線。除了philips公司,像 motorola公司,韓國三星,日本三菱,美國 a/d等許多大公司都陸續推出了帶有i2c總線標準接口的產品,涉及微處理器(mcu),通用的外圍設備(eeprom,i/o口,a/d,d/a ,lcd/led顯示器,日歷時鐘,鍵盤,打印機接口等等)和家電、音像產品。i2c總線的應用日益廣泛,i2c總線器件的接口電路設計也顯得十分重要。

本文引用地址:http://www.104case.com/article/201612/329454.htm2 i2c總線簡介[1]

自從philips推出i2c總線標準以來,經歷了3個版本:version 1.0-1992,version2.0-1998和version 2.1-2000。這使得i2c總線標準不斷完善,應用范圍日益廣泛。i2c總線標準規定有如下3種工作模式:

(1) standard-mode(標準模式):線上最快傳輸速率為100kbps

(2) fast-mode(快速模式):線上最快傳輸速率為400kbps

(3) hs-mode(high-speed mode,高速模式):線上最快傳輸速率為3.4mbps

(4) 這3種工作模式可以向前兼容,即hs-mode環境下允許以f/s-mode(fast or standard-mode)工作,fast-mode環境下允許以standard-mode工作。實際電路中的具體工作模式主要取決于系統中i2c器件接口的電氣特性。

i2c總線技術采用器件地址的硬件設置方法,通過軟件尋址完全避免了器件片選線尋址的方法,從而使得硬件系統具有最簡單而靈活的擴展方法。隨著i2c技術的廣泛應用,傳統的7位從器件地址(slaver addresses)已經無法滿足實際需要,在改進的i2c總線標準中增加了10位從地址尋址技術,這樣可以把從器件地址由原來的100多個擴充為 1024個,為i2c總線技術的廣泛應用奠定了基礎。

目前,實際應用的i2c器件都以f/s-mode 和7位從地址標準為主。關于hs-mode 的應用和10位從地址的設計方法可以參閱文獻1。

3 i2c總線協議要求[1,2]

i2c總線協議有嚴格的時序要求。總線工作時,由時鐘控制線scl傳送時鐘脈沖,由串行數據線sda傳送數據。總線傳送的每幀數據均為1個字節 (8bit),但啟動i2c總線后,傳送的字節個數沒有限制,只要求每傳送1個字節后,對方回應1個應答位(acknowledge bit)。在發送時,首先發送的是數據的最高位(msb)。協議規定,啟動總線后的第1個字節的高7位是從器件的尋址地址(硬件地址),第8位為方向位 (“0”表示主器件對從器件的寫操作;“1”表示主器件對從器件的讀操作),其余的字節為操作的數據。總線每次傳送開始時有起始信號,結束時有停止信號。在總線傳送完1個或幾個字節后,可以控制scl線的電平變低,從而使傳送暫停。

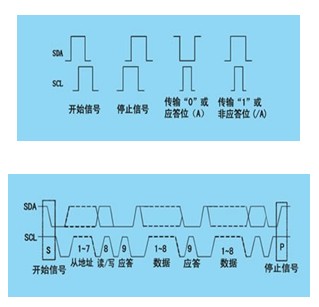

圖1列出了i2c總線上典型的幾個信號時序,圖2表示了i2c總線上1次完整的數據傳送過程。

在i2c總線系統中,信號傳輸的具體時序描述如下:

(1) 起始信號(s):在時鐘scl為高電平期間,數據線sda出現由高電平向低電平的變化,啟動i2c總線;

(2) 停止信號(p):在時鐘scl為高電平期間,數據線sda出現由低電平向高電平的變化,停止i2c總線上的數據傳送;

(3) 應答信號(a):i2c總線的第9個脈沖對應應答,對應sda線上顯示低電平時為“應答”信號(a),sda線上顯示高電平時為“非應答”信號(/a);

(4) 數據位傳送:i2c總線開始信號或應答信號之后的第1~8個時鐘脈沖對應一個字節的8位數據傳送。在脈沖高電平期間,數據串行傳送;在脈沖低電平期間,數據準備,允許總線上數據電平變化。

4 i2c總線的接口擴展技術

i2c總線軟硬件協議十分巧妙,它可以用于構成多主系統。系統中有多個i2c總線接口單片機時,會出現多主競爭的復雜狀態。i2c總線軟硬件協議,以及 i2c總線單片機中的sfr寄存器保證了多主競爭時的協調管理。i2c總線提供的狀態處理軟件包能自動處理總線上出現的26種狀態。在使用i2c總線時,將這些軟件在程序存儲器中定位,利用這些軟件編制出歸一化的操作命令,設計起來十分簡單,方便。對沒有i2c總線接口的單片機,要構成多主系統,幾乎不可能。因此,在多主的i2c總線系統中,一定要使用帶i2c總線接口的單片機[7]。

在單主方式的i2c總線系統中,總線上只有一個主器件,其余都是帶有i2c總線的外圍器件。由于總線上只有一個主器件成為主節點,該主器件永遠占據總線,不會出現總線競爭,主節點也不必有自己的節點地址。在單主系統中,主器件可以是沒有i2c總線接口的器件,此時用它的兩根i/o口線來虛擬i2c總線接口,只要時序滿足i2c總線的要求,就可以進行i2c總線操作。

4.1基于單片機系統的i2c總線接口技術[2,3]

i2c總線技術最早是基于單片機系統提出的,現在越來越多的單片機帶有i2c總線接口,可以直接應用。但是更多的單片機系統并沒有i2c總線接口,要在 i2c總線系統中應用,必須進行i2c總線虛擬。這一技術經過多年的發展,已經十分成熟,具有專門的虛擬通用軟件包viic1.0[3],用戶甚至可以不必了解i2c總線的協議,也可以進行i2c總線開發,實現了操作的“傻瓜化”,極大的方便了用戶,擴展了單片機的應用領域,推動了i2c總線技術的發展。

該軟件包適用于80c51系列單主系統中i2c總線外圍器件擴展的應用程序設計。由于軟件中的時序模擬基于6mhz時鐘設計,故在實際應用中可以根據具體的系統時鐘來適當修改時序模擬子程序中的空操作指令,便可以直接應用。

該軟件包包含以下3部分共9個子程序:

(1) 模擬i2c總線操作的典型時序:起始位(star)、停止位(stop)、發送應答位(mack)、發送非應答位(mnack) 。

(2) 模擬i2c數據傳送過程:應答位檢查(cack)、發送1個字節數據(wrbyt)、接收1個字節數據(rdbyt)。

(3) 模擬外圍器件讀寫操作:i2c總線讀操作過程(rdnbyt)(接收n個字節),i2c總線寫操作過程(wrnbyt)(發送n個字節)。

不論總線上擴展什么外圍設備,都統一采用以下3條指令作為viic軟件包與用戶的操作接口界面,即:

mov sla,#slar/slaw;總線上節點尋址并確定傳送方向

mov numbyt,#n;確定傳送字節數n

lcall rdnbyt/wrnbyt;讀/寫操作調用

文獻中對該虛擬軟件包有詳細的介紹,包括源程序和使用說明,并給出了應用實例。

對應該軟件包,文獻4中介紹了基于franklin c51編寫的虛擬i2c總線軟件包viicc1.0。它由1個頭文件和1個源程序組成。在使用時,用戶同樣不必關心i2c外圍器件功能如何,都使用下面的指令:

rdnbyt(uchar slar,uchar qq[],uchar number); ――單主系統的主接收方式

wrnbyt(uchar slaw,uchar ff[],uchar number); ――單主系統的主發送方式

其中:

slar/slaw是從器件的地址 (讀/寫);

number是需要讀寫的數據字節的個數;

qq[]是從虛擬i2c總線上讀出的數據數組;

ff[]是需要向虛擬i2c總線上寫入的數據數組。

viicc1.0占用資源與viic1.0占用資源基本上一樣。由于viicc1.0是基于 12mhz的時鐘設計的,因此實際系統時鐘變化時,需要在頭文件中適當修改nop ( )的個數。實際應用時,只要把頭文件和源程序寫入相應的程序區,適當修改幾個參數就可以應用,操作簡單方便。

4. 2 基于dsp系統的i2c總線接口的擴展

如前文所述,i2c總線技術在以單片機為mcu的系統中應用最廣泛,設計也最靈活簡單。但在許多的系統中,采用dsp(數字信號處理器)作為mcu。若系統中含有i2c接口的外圍器件,我們也可以直接用dsp進行i2c總線的開發。目前還沒有專門帶有i2c接口的dsp,所以也只能采用dsp的2根i/o 口線進行模擬。仿照文獻3,4中的設計思路,文獻5給出了基于tms320c2xx系列dsp的虛擬i2c總線軟件包的設計和應用,極大的方便了以dsp 為mcu的i2c系統。

該軟件包含有2個宏定義和12個子函數,適用于單主系統的主發送和主接收方式,支持tms320c2xx系列對i2c總線外圍器件n字節的讀寫操作,通信方式為對虛擬節點尋址后點對點的讀寫。該軟件包采用4根通用i/o口線(i/o0~i/o3)的任意2根模擬sda和scl,他們的輸入輸出方向由 aspcr的低4位設定,相應口線狀態的設定或讀取由iosr寄存器控制。由于c2xx系列的dsp結構與單片機有很大的不同,口線的輸入輸出狀態不是自動切換的,且aspcr 、iosr寄存器都不支持位尋址方式,所以該軟件包與前文基于單片機的軟件包viic1.0/viicc1.0有所不同。對用戶而言,可不必了解軟件細節,只要正確設置相應存儲單元的內容,調用相應的子函數就可以應用,用戶接口同樣簡單易用。

另外,文獻[6]給出了tms320vc5402實現i2c總線接口的2種設計思路。一是利用該型號dsp的多信道緩沖串口(mcbsp):通過設置 mcbsp的spcr1、spcr2和pcr 相應位,可以將mcbsp的clkr、fsr、clkx、fsx腳設置為通用i/o腳,然后按照i2c總線協議進行軟件編程,就可以實現與i2c總線的接口;二是利用vc5402 的主機接口(hpi):通過設置hpi控制寄存器(hpic)、通用目的i/o狀態寄存器(gpiosr)和通用目的i/o控制寄存器(gpiocr)相應位,就可以將8位的數據總線(hd0~hd7)轉變成通用i/o口,然后進行編程,同樣可以實現與i2c總線的接口。文獻中給出了較詳細的設計思路和部分程序代碼。

評論