基于測試系統的FPGA測試方法研究

1 引言

本文引用地址:http://www.104case.com/article/201612/328517.htm目前FPGA大多采用基于查找表技術,主要由可編程輸入/輸出單元(IOB)、可編程邏輯單元(CLB)、可編程布線資源(PI)、配置用的SRAM、BlockRAM和數字延遲鎖相環(DLL)等部分組成。對FPGA進行測試要對FPGA內部可能包含的資源進行結構分析,經過一個測試配置(TC)和向量實施(TS)的過程,把FPGA配置為具有特定功能的電路,再從應用級別上對電路進行測試,完成電路的功能及參數測試。

2 FPGA的配置方法

對FPGA進行配置有多種方法可以選擇,包括邊界掃描配置方法、Xilinx公司專用的SPI/BPI FLASH配置方法、System ACE配置方法、CPLD+第三方FLASH配置方法、系統直接加載配置向量的配置方法。邊界掃描方法主要適合在線配置調試用,Xilinx專用Flash配置方法,每次只能在FLASH中存儲一段配置碼,不適合反復配置測試過程。System ACE方法需要專門的System ACE控制芯片和CF卡,應用比較麻煩。比較適合系統測試的主要是后兩種方法。

2.1 測試系統直接配置方法

當采用的測試系統比較高級,比如Teradyne公司的UltraFLEX,該系統測試頻率高達500 MHz,測試通道數多達1024個,測試向量深度可達128 M,可以使用系統直接加載二進制配置向量對FPGA進行配置。

能夠在同一個操作流程中完成FPGA芯片的多次“配置-測試”過程。該方法操作簡單,提高了FPGA芯片的測試效率,能夠實現FPGA芯片的產業化測試。

2.2 CPLD+第三方FLASH的配置方法

當待測FPGA的配置代碼比較大,而測試系統(ATE)向量深度不足時,可以采用 CPLD+第三方FLASH的配置方法,其結構圖如圖1所示。

其中CPLD的設計是最重要的部分,它所實現的功能模塊包括接口模塊、控制模塊、地址發生器模塊。接口模塊實現與測試系統的通信,接收測試系統指令并作相應處理,同時將工作狀態反饋給測試系統;控制模塊提供控制時序命令,操縱整個配置過程;地址發生器模塊為讀取閃存數據提供數據地址。CPLD內部各功能模塊采用硬件描述語言實現。

Flash是配置文件的存儲器件,預先將多段16進制格式配置文件燒寫進Flash中。FPGA是系統中配置的目標器件。

本方法采用ATE控制CPLD讀取FLASH中不同地址范圍內的配置代碼對FPGA進行配置,再在不掉電的情況下對配置好的FPGA進行功能和參數測試。

3 FPGA配置模式選擇與配置碼的生成

3.1 FPGA配置模式選擇

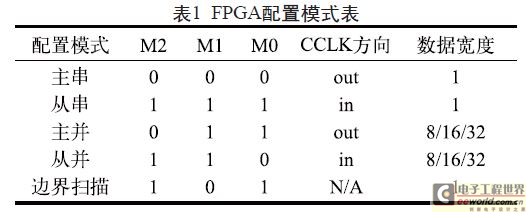

FPGA的配置模式有多種,而且不同系列FPGA的配置模式有一定的差別,主要的配置模式有:主串模式、從串模式、主并模式、從并模式和邊界掃描模式。通過設置三個模式選擇管腳M0、M1、M2可以選擇不同配置模式。配置模式如表1所示。

用測試系統對FPGA進行測試大部分時間是用在配置上,配置時間根據配置碼大小不同可達幾毫秒到數十秒。為了提高配置速度,我們對FPGA進行配置選擇從并模式,可以最大地節省測試配置時間。以Virtex-II系列FPGA為例,其從并配置模式原理圖如圖2所示。

3.2 配置碼的生成

3.2 配置碼的生成FPGA配置碼要在Xilinx ISE開發環境下編寫配置程序,生成所需要的二進制格式配置文件,如圖3所示。

圖中1~7行屬于文件頭,需要刪除掉,第8~9行就是配置數據開始標志:FFFFFFFF AA995566,后面的都是配置數據。

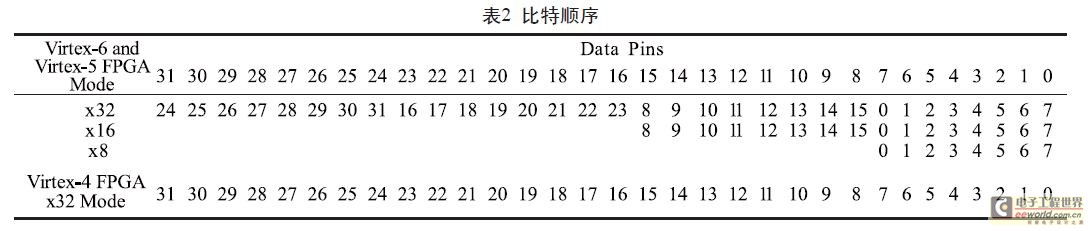

配置文件數據寬度都是32位,還要根據不同系列FPGA的配置數據寬度進行修改。以Virtex-II系列為例,它的從并模式數據寬度是8位,我們需要編寫應用程序轉化成8位寬的數據。配置數據比特順序如表2所示,以8位寬數據為例,其D0為最高位。

4 FPGA的配置與測試流程

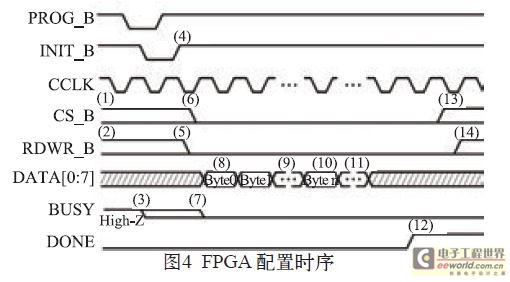

FPGA配置過程主要有四個步驟:清除配置存儲器、初始化、配置和啟動。以Virtex-II FPGA為例,配置過程的時序要求如圖5所示:系統上電后給PROG_B管腳一個低信號,FPGA便開始清除配置存儲器,FPGA內部將INIT_B管腳和DONE管腳拉低。當配置存儲器清除完畢,INIT_B會變高,之后若CS_B為低有效,就可以傳送配置數據對FPGA進行配置,當管腳DONE由低變為高,便標志芯片的配置完成。

用測試系統對FPGA進行測試可以把配置代碼和測試代碼分別做成不同的Pattern文件,把配置過程也作為一個功能測試項,這樣便可對被測FPGA電路進行反復的配置--測試。配置pattern文件如圖5所示。

FPGA配置完畢后,便具有一定的功能,可以像其他電路一樣進行功能和參數測試。

5 結論

本文詳細介紹了FPGA配置方法、配置模式選擇和配置碼的生成方法,并以Virtex-II系列FPGAXC2V250為例詳細介紹了用測試系統Ultra-FLEX對FPGA的配置與測試過程。 該方法可廣泛應用于各種FPGA的測試,具有較強的通用性,對于實現FPGA的產業化測試具有重要意義。

評論