EMCCD相機數字控制系統的VHDL設計

電荷耦合器件(CCD)現在廣泛應用于天文圖像。

傳統的CCD讀出較慢且在高幀率的情況下有很高的讀出噪音,這限制了它在高時間分辨率天文學的應用。

21世紀初,英國的E2V 公司和美國TI公司各自獨立地研發了一種具有新型讀出結構的CCD 器件,即電子倍增CCD(Electron Multiplying Charge Coupled Device),簡記為EMCCD.這是新一代高質量微光成像器件。與傳統的CCD相比,它采用了片上電子增益技術,利用片上增益寄存器使圖像信息在電子轉移過程中得到放大,這使得它在很高的讀出速率下仍具有相對很低的讀出噪聲,能在微光源下高分辨率成像。

EMCCD 的這些特性,使得它能對微弱光信號進行快速的成像。近年來EMCCD被越來越多地運用到了天文觀測,國外研究人員采用E2V 公司的EMCCD 器件L3 VISION CCD設計的相機取得了極好的觀測效果,并進行了光子技術成像實驗。而國內對天文用EMCCD相機的研制與應用還處于起步階段。目前,實驗室正在研制一套基于EMCCD的二維天文光子計數實驗成像系統,該成像系統可使用TI公司的EMCCD 器件TC253和TC285作為圖像傳感器。

本文針對使用TC253器件構成的圖像采集系統,主要介紹EMCCD的數字控制方案和設計方法。由于硬件系統使用Altera公司EP3C16Q240C8N FPGA芯片,所以該數字系統是在Altera Quartus Ⅱ 8.0開發環境下采用VHDL語言來進行設計并實現整個系統的數字控制部分。本文闡述了該數字控制系統的設計思想以及VHDL 的實現過程,給出了關鍵信號的仿真與實測波形,并對結果進行了分析。

1 EMCCD圖像傳感器與模擬信號處理器的

控制要求

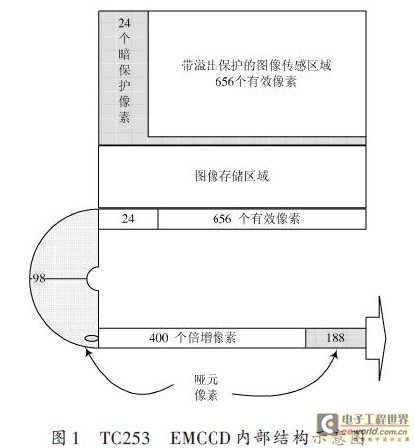

TC253 是一款具有680(H)×500(V)像素的幀轉移CCD圖像傳感器,其結構圖如圖1所示。它被廣泛的應用于要求高靈敏度、低噪聲并且小尺寸的特殊用途的成像系統之中。該圖像傳感器的像素尺寸為7.4 μm×7.4 μm,具有快速單脈沖清除能力,以及逐行掃描、隔行掃描、行合并三種讀出模式。在本系統設計中,使用的是逐行掃描模式。

TC253 屬于幀轉移結構的EMCCD 器件,其面陣分為圖像傳感區(亦稱成像區)和存儲區兩部分,如圖1所示。上電工作時,光學影像照射到圖像傳感區的像素上,對應像素的勢阱會產生并收集電子,形成一幅電子影像。在曝光結束以后,這幅電子影像在成像區和存儲區的垂直時鐘驅動下快速轉移到圖像存儲區域。此后該電子影像在存儲區的垂直轉移時鐘的驅動下,逐行地轉移到水平寄存器中,并在水平轉移時鐘的驅動下,通過水平串行寄存器轉移到輸出放大器。TC253 的水平串行寄存器分為前后兩部分,前一部分與其他CCD 圖像傳感器的設計一樣;后一部分則是獨特的,包含400個級聯的電子倍增寄存器,在這些倍增寄存器前后還有一些過渡的啞元像素,具體級數與位置如圖1 所示。

這400個級聯的倍增寄存器是該器件最具特色的部分,根據所施加的倍增電極電平高低和工作溫度,可以進行電子影像的放大。要使EMCCD能夠準確無誤的讀出光電圖像,需使光電子能有序地進行垂直與水平的交替轉移,并通過放大與相關雙取樣(CDS)電路進行模擬信號處理,最后經模/數轉換器(ADC)輸出。因此,必須按照EMCCD 以及CDS 和ADC 的數據手冊所述的驅動時序來進行相關時鐘的時序設計。EMCCD TC253 一共有4 個時鐘驅動信號,4 個垂直轉移信號(IAG1,IAG2,SAG1,SAG2),3 個水平轉移信號(SRG1,SRG2,CMG),一個曝光溢出控制信號(ODB)。在本系統中,為簡化CCD模擬信號處理電路的設計,使用了單片模擬信號處理器AD9845B 作為CCD 輸出模擬信號的放大、CDS 和ADC電路。

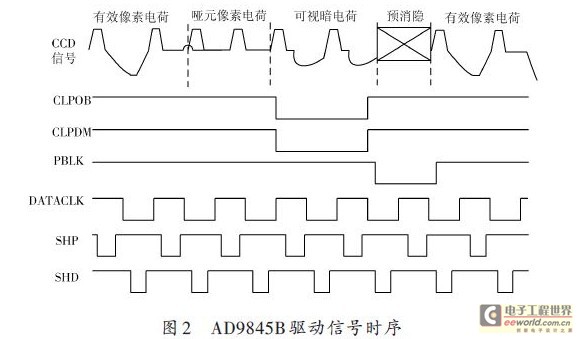

模擬信號處理器AD9845B是一款針對CCD應用的處理器AD9845A 的升級版,亦稱為模擬前端處理器(AFE)。它具有30 MHz單通道結構,用于面陣CCD 隔行掃描和逐行掃描信號的調理和采樣[8].根據其與CCD對應的時序關系,共需要設置6個時鐘驅動信號,分別是相關雙采樣采集參考電平的時鐘SHP、相關雙采樣采集數據信號電平的時鐘SHD、讀出數據時鐘DATACLK、黑電平箝位時鐘CLPOB、輸入箝位時鐘CLPDM 以及消隱數據時鐘PBLK[9].6個驅動信號按照圖2所示的時序進行設置,這與AD9845B 數據手冊所提供的時序稍有不同。

2 數字系統總體設計思想

由EMCCD 和ADC 的數據手冊并結合該項目的要求可知,該數字控制系統就是要實現EMCCD圖像傳感器在幀轉移讀出模式和ODB清零模式下的驅動時鐘信號,以及在幀轉移讀出模式下,驅動ADC正常工作的時鐘信號。幀轉移讀出模式有4種水平讀出頻率,分別為12.5 MHz,6.25 MHz,3.125 MHz,1.562 5 MHz,標準讀出頻率為12.5 MHz,另外三種讀出頻率,為了對比測試圖像采集的效果而設置的。同時要求可以控制曝光積分時間,選擇是否超越讀出(Overscan)。根據VHDL語言的特點,采用頂層模塊控制底層模塊的方式,即以頂層邏輯控制各個底層邏輯的方式來實現該數字控制系統的功能。這種設計思想在實驗室設計的RDCCD 相機[10]、KAISS 相機[11] 中都使用過,控制效果良好,程序結構清晰。

在頂層模塊中,定義了一些與底層模塊連接的端口,以及數字控制系統與外部硬件連接的端口,設置了頂層模塊與各底層模塊端口匹配的方式。生成了各個模塊需要的各種時鐘信號。以及協調了幀轉移讀出模式與ODB清零模式的切換。

在底層模塊中主要是兩個子模塊:ODB 清零和幀轉移讀出。每個子模塊都有其獨立的輸入時鐘信號與輸出端口,在相應模塊被選中執行時能順利完成各自任務,生成正確的輸出時鐘信號。

3 數字系統的實現與仿真

該設計是在Altera Quartus Ⅱ 8.0的開發環境下,分別對頂層模塊和底層模塊進行VHDL編程設計與仿真的。下面將介紹各模塊的具體設計、仿真過程和一些實現技巧。

3.1 頂層模塊的設計

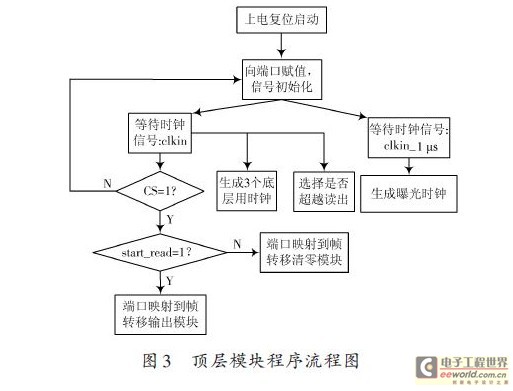

頂層模塊中定義了一些輸入端口、輸出端口和一些與底層模塊連接用端口及其映射關系,生成了底層模塊需要的各種時鐘信號,設置了各模塊的切換條件。以clkin作為輸入主時鐘,生成了3個底層用時鐘:清零時鐘clock_C,垂直轉移時鐘clock_V、水平轉移時鐘clock_H;以clkin_1 μs作為另一輸入時鐘,生成曝光階段時鐘clock_1 μs.還設置了“cs”,“read_select”,“start_read”三個判斷信號,用于選擇、切換ODB清零與幀轉移讀出模式。在Quartus Ⅱ中編譯成功后生成頂層模塊,命名為top.頂層模塊的VHDL 程序流程圖如圖3所示。

3.2 底層模塊的設計

底層模塊包含ODB清零子模塊與幀轉移讀出子模塊,有時亦稱為ODB 清零工作模式與幀轉移讀出工作模式。下面分別介紹這兩個子模塊的具體設計過程與仿真結果。

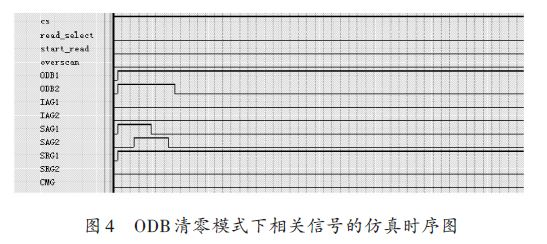

3.2.1 ODB清零模式由頂層模塊流程圖(即圖3)可知,當片選信號cs='1',并且read_select='0‘時,系統將運行ODB 清零模塊。該模塊就是在系統上電后或CCD未進入曝光工作狀態時對CCD 成像區的殘余電荷進行清除。根據TC253的數據手冊,曝光溢出控制信號ODB在整個圖像采集過程中有三個電平值,溢流控制階段為5.3 V,清零階段為12.5 V,電荷轉移階段為4.8 V.因此在具體的VHDL編程過程中,可以生成ODB1,ODB2兩個信號,將它們輸出到一個ODB 驅動電路中,可形成ODB 控制信號。

該模塊以頂層生成的時鐘信號clock_C作為參考時鐘,當清零使能信號start_read='0’時,開始ODB清零過程。在此過程中,垂直轉移信號SAG1、SAG2運行一個周期。圖4 為該子模塊VHDL 程序的仿真結果。通過對比TC253的數據手冊可知,仿真波形與該器件要求的時序是一致的。

3.2.2 幀轉移讀出模式

根據TC253 的數據手冊,將該EMCCD 器件的成像與幀轉移讀出模式劃分為4個階段,按順序分別是清零階段S1、曝光階段S2、垂直轉移階段S3、水平輸出階段S4.在頂層生成的4個時鐘信號,分別用作這4階段的控制時鐘,使之能夠準確地形成并輸出滿足TC253所需的各信號。

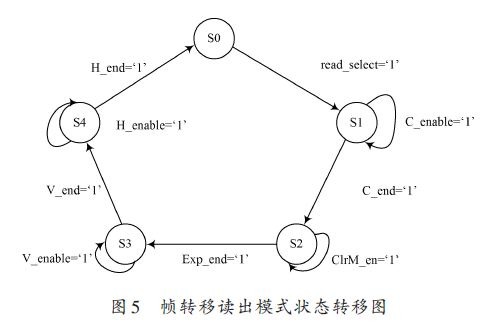

為了能使4 個階段的信號順序執行、互不沖突,在VHDL 程序代碼中,需要設置必要的判定信號,以控制狀態的轉移。這4個階段的狀態轉移圖如圖5所示。由圖可知,系統上電后進入初始狀態S0,當read_select='1‘時,進入幀轉移讀出模式。當使能信號C_enable='1’時,進行成像區電荷清除S1,直到結束標志位C_end='1‘后進入曝光階段S2;當曝光使能位ClrM_en='1’時,開始曝光,直到結束標志位Exp_end='1‘后進入垂直轉移階段S3;當垂直轉移使能位V_enable='1’時,開始垂直轉移,直到結束標志位V_end='1‘后進入水平輸出階段S4;當水平輸出使能位H_enable='1’時,開始水平輸出,直到結束標志位H_end='1‘后回到初始狀態S0.

為了能正確輸出數字圖像,在水平輸出階段,還需要對模擬信號處理器AD9845B 進行控制。為此,在此階段(S4),需要根據AD9845B 的時序要求(見圖2),產生并輸出該器件要求的DATACLK,SHP,SHD,PBLK,CLPDM,CLPOB信號波形。

圖6 為幀轉移模式下主要信號的仿真結果。按TC253 實際的幀轉移行數680 和水平寄存器數目500,仿真波形將很長,無法顯示。由于仿真的目的是驗證邏輯和時序關系,因此,在仿真時我們將幀轉移行數和水平寄存器數目分別設定為10 和10,才獲

評論