使用低成本FPGA巧妙地?cái)U(kuò)展微處理器的連接

微處理器連接的挑戰(zhàn)

本文引用地址:http://www.104case.com/article/201612/327761.htm在現(xiàn)代電子系統(tǒng)設(shè)計(jì)中,微處理器是不可缺少的一個(gè)部件。然而,隨著系統(tǒng)變得越來(lái)越復(fù)雜,擁有更廣泛的功能和用戶接口時(shí),使用中檔微處理器的系統(tǒng)架構(gòu)在連接一個(gè)或多個(gè)微處理器時(shí)面臨著三個(gè)關(guān)鍵的挑戰(zhàn):

?運(yùn)行超過(guò)150個(gè)通用I/O(GPIO);

?在100至150個(gè)GPIO范圍內(nèi)

尋找符合成本效益的解決方案;

?匹配系統(tǒng)所需要的I/O外設(shè)。

采用FPGA(現(xiàn)場(chǎng)可編程門陣列)可以很容易地應(yīng)對(duì)這些挑戰(zhàn),在過(guò)去10年里,F(xiàn)PGA的成本和功耗已經(jīng)大幅下降,使它們非常適合于各種大批量、低成本的應(yīng)用,包括移動(dòng)電子產(chǎn)品。

微處理器連接的回顧

對(duì)中檔微處理器的回顧揭示了三種常見的連接特性。首先,大多數(shù)系列GPIO的數(shù)量被限制在100和150之間;其次,每個(gè)GPIO的價(jià)格曲線不是線性的,通常在100個(gè)GPIO左右時(shí),每個(gè)GPIO的成本迅速增加;第三,雖然大多數(shù)微處理器提供一些連接外設(shè),如UART、SPI和I2C,但外設(shè)的數(shù)量和可用的組合是有限的。

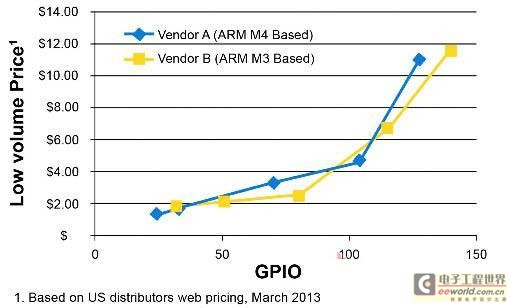

圖1展示了源于美國(guó)分銷商的信息,針對(duì)兩個(gè)通用的中檔微處理器,一種基于ARM M3內(nèi)核,另一種ARM M4內(nèi)核,圖中說(shuō)明了GPIO選擇的典型范圍和與之相關(guān)的小批量的定價(jià)。這兩個(gè)系列都顯示出在100個(gè)GPIO附近的價(jià)格拐點(diǎn),以及總的GPIO所受的限制。

FPGA技術(shù)的回顧

在過(guò)去的20年中,F(xiàn)PGA技術(shù)提供了一種能夠快速實(shí)現(xiàn)連接擴(kuò)展的方法,但這些器件的成本和功耗限制了這種方法的應(yīng)用。盡管如此,F(xiàn)PGA的功耗和成本的降低充分地證明了摩爾定律。在1995年,相當(dāng)于現(xiàn)在的256個(gè)查找表(LUT)FPGA的成本超過(guò)50美元。而現(xiàn)在有此功能的最新器件的成本僅為0.50美元。功耗的改進(jìn)同樣可觀。對(duì)于示例的器件,在1995年典型的靜態(tài)功耗為0.5W,如今已降至的50μW。這些趨勢(shì)如圖2所示。

圖1 中檔微處理器I/O的選擇

圖2 FPGA成本相對(duì)于功耗的趨勢(shì)

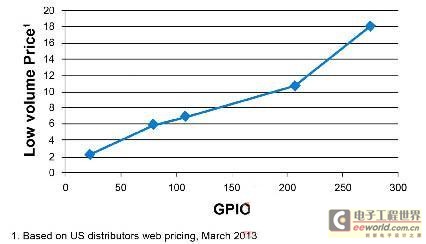

圖3 低成本FPGA的I/O特性

低成本FPGA提供了眾多的I/O數(shù)。例如,萊迪思超低密度MachXO2提供了從22到超過(guò)250個(gè)I/O的數(shù)量。如圖3所示,對(duì)應(yīng)I/O范圍的價(jià)格是相當(dāng)線性的,根據(jù)一家美國(guó)分銷商的信息,圖中示出了小批量的價(jià)格。

除了邏輯和I/O之外,MachXO2提供了一些可以幫助建立功能的模塊,以便擴(kuò)展微處理器的連接。這些包括嵌入式RAM塊(EBR)、鎖相環(huán)(PLL)和提供固化模塊的嵌入式功能塊(EBR),諸如SPI、2×I2C,以及定時(shí)計(jì)數(shù)器和用戶閃存。

接口的實(shí)現(xiàn)方法

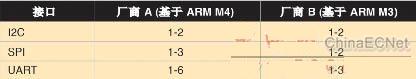

微處理器連接的主要方式是UART以及SPI和I2C總線。絕大多數(shù)的中檔微控制器提供了數(shù)量有限的這些大量使用的接口。圖4指出了前一節(jié)中重點(diǎn)所述器件所提供的這些接口的數(shù)量。

當(dāng)一個(gè)設(shè)計(jì)所需的接口數(shù)量比微處理器所能提供的更多時(shí),設(shè)計(jì)師可以采取兩種常用的方法:

?微處理器控制GPIO(稱為位拆裂)

?在FPGA中用硬件實(shí)現(xiàn)

位拆裂方法有三個(gè)明顯的缺點(diǎn):首先,接口操作的速度可能被限制到低MHz范圍,微處理器無(wú)法快速地控制I/O引腳的狀態(tài);其次,由于額外的工作量和微處理器可以保持在低功耗睡眠模式的時(shí)間的減少,微處理器的功耗增加了;第三,由于微處理器本質(zhì)上是有限的時(shí)序精度,除了采用非常低的速度,實(shí)現(xiàn)異步UART型接口變得不可能。

一片綜合的FPGA實(shí)現(xiàn)這些接口可能用大約250個(gè)LUT,用優(yōu)化版本實(shí)現(xiàn)約100個(gè)LUT。根據(jù)所用FPGA的功能,在適當(dāng)?shù)慕M合下可以輕松實(shí)現(xiàn)數(shù)10個(gè)額外的接口。由于FPGA的硬件性質(zhì),執(zhí)行速度高達(dá)幾十MHz是很容易實(shí)現(xiàn)的。FPGA中還可以實(shí)現(xiàn)緩沖和智能中斷,可以允許微處理器有更多的時(shí)間處于睡眠模式下,以便降低整個(gè)系統(tǒng)的功耗。

巧妙實(shí)施連接擴(kuò)展的實(shí)例

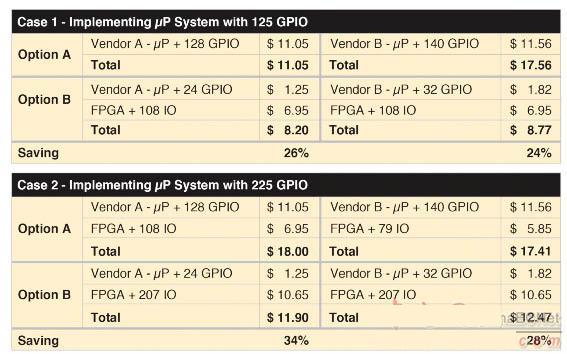

通過(guò)對(duì)微處理器和FPGA進(jìn)行巧妙地配置連接,設(shè)計(jì)師可以在他們的系統(tǒng)中實(shí)現(xiàn)所需的連接,同時(shí)降低整體成本。圖5中使用之前所述的價(jià)格數(shù)據(jù)對(duì)采用這種策略的成本進(jìn)行了調(diào)查。可以看到通過(guò)最大化地利用FPGA,連接擴(kuò)展成本可以減少24%至34%。

低成本、低功耗FPGA讓您可以重新考慮系統(tǒng)的劃分

在過(guò)去的15年中,F(xiàn)PGA的成本和功耗下降了2個(gè)數(shù)量級(jí)。這些改進(jìn)特性使設(shè)計(jì)師能夠重新思考如何實(shí)現(xiàn)微處理器的連接。通過(guò)對(duì)FPGA和微控制器之間的巧妙配置,現(xiàn)在設(shè)計(jì)師可以降低成本和功耗,同時(shí)提高性能和靈活性。

圖4 微處理器可用的接口

圖5 巧妙實(shí)施系統(tǒng)配置的實(shí)例

評(píng)論