一種用于FPGA的改進算法弱化了方波重影

0 引言

本文引用地址:http://www.104case.com/article/201612/327591.htmDDS(Direct Digital Frequency Synthesis)頻率合成器能夠很方便地輸出任意波形[1],方波作為最常用波形之一,具有其特殊性。但輸出的方波存在明顯的重影現象直接影響了方波的質量。

1 方波重影出現的原因

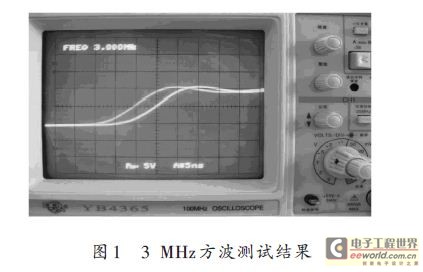

假設系統時鐘頻率為200 MHz,以輸出3 MHz方波為例,從模擬示波器觀察到的結果如圖1所示。

圖1中存在明顯的雙邊沿現象,且兩條上升沿的間距為5 ns,剛好等于系統時鐘的周期。這種現象可稱為方波重影。

根據DDS的工作原理可知,相位序列具有周期性[2].

在相位序列的一個周期內,相位累加器會溢出若干次,并且每次溢出后的殘留量都不一樣。當殘留量足夠大時,再次發生溢出所需的累加次數會減少一次。累加次數的減少,意味著方波的周期變小。不同周期的方波疊加在一起,便出現重影現象。

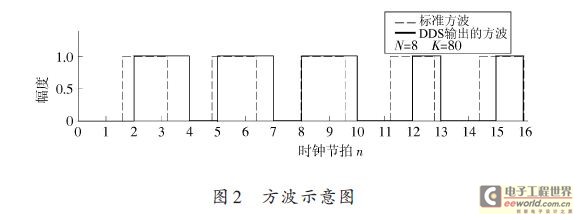

使用Matlab模擬DDS生成方波的過程,可以得到更直觀的認識,如圖2所示。

按照圖2中的參數設置,方波的周期等于:

從圖2可以看出,為了輸出周期為3.2Tc 的方波,在相位序列的一個周期內,DDS 頻率合成器的實際輸出為:一個周期為4Tc 且占空比為50%的方波,兩個周期為3Tc 且占空比為75%的方波,兩個周期為3Tc 且占空比為25%的方波。從平均的意義上看,剛好組成周期為3.2Tc 且占空比為50%的方波。因此,DDS 頻率合成器輸出的方波不僅周期在波動,而且占空比也發生波動。

如果將DDS 頻率合成器看成分頻器,在滿足奈奎斯特采樣定理[4]的條件下,可以得出如下結論:輸出正弦波等連續信號時,DDS可以實現任意比例的分頻;輸出方波等存在跳變沿的信號時,這類信號的周期只能是系統時鐘周期的整數倍,否則出現重影。

2 方波改進算法的研究與實現

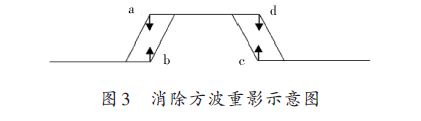

為了解決方波重影問題,可從時域的角度分析。將若干個不同周期的方波疊加到一起,可得示意圖如圖3所示。

圖3 中,使a 點和d 點向下抖動,使b 點和c 點向上抖動,多次疊加后可有效弱化方波重影,甚至徹底消除。但是,如何準確地判斷a、b、c、d 四個點,成為實現這一方法的最大障礙。

仔細觀察圖3和圖2,引入時鐘節拍的概念,便能找到依據判斷a、b、c、d四個點。首先,定義方波的周期和上升沿時刻,以50%占空比為例,這兩個數值可分別表示為:

其中,ceil表示朝正無窮方向取整,floor表示朝負無窮方向取整,均為Matlab運算符[5].

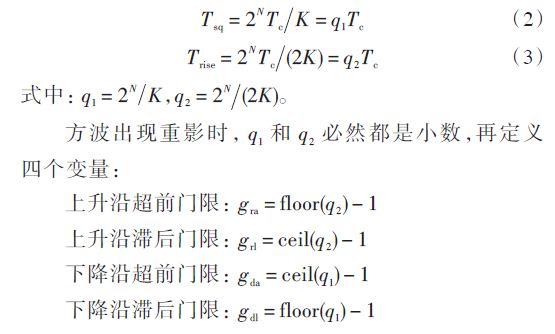

當系統時鐘的頻率為200 MHz時,以輸出3 MHz方波為例,計算結果如表1所示。

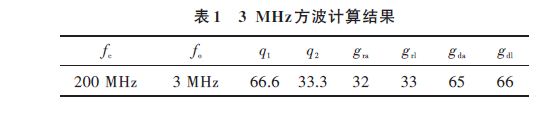

類似于圖3,3 MHz方波的示意圖如圖4所示。

從圖4 可以看出,a 點和b 點發生在時鐘節拍為33的位置,c點和d點發生在時鐘節拍為65的位置。當出現c點時,意味著本次方波的周期較小,下一個時鐘節根據圖3 的規律,在時鐘節拍為grl 和gda 的位置,利用原始方波信號的高低電平信息,就能得到a、b、c、d四個點。假設DAC的位數為14位,方波改進算法的實現過程可分為以下三個步驟:

第一步,定義一個計數器,并以相位累加器的進位輸出信號作為清零信號,即相位累加器每溢出一次,該計數器就清零一次。因此,該計數器的計數值就表示圖4中的時鐘節拍。

第二步,定義一個狀態機,假設計數器的計數值為num,簡化后的狀態轉移圖如圖5所示。

狀態RISE標記的時鐘節拍是grl,處于此狀態時,如果原始方波信號為高電平,便得到a點;如果原始方波信號為低電平,便得到b點。狀態DOWN標記的時鐘節拍是gda,處于此狀態時,如果原始方波信號為低電平,便得到c點;如果原始方波信號為高電平,便得到d點。

第三步,定義一個隨機變量random,random的變化范圍是0~2 048,可通過11位m序列實現之。使用verilog語言的位拼接運算符[6],在a 點和d 點將送給DAC 的數據定義為10 240 加random,即“{3'b101,random}”;在b 點和c 點將送給DAC 的數據定義為4 096 加random,即“{3'b010,random}”.

3 測試與總結

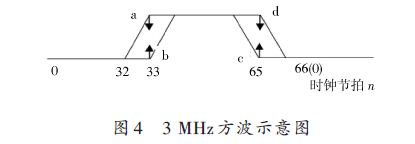

使用新的方波算法后,可得測試結果如圖6所示。

對比圖6和圖1可以看出,方波重影的寬度從5 ns縮短至3 ns,并且上升沿呈實心狀,不再由兩條邊沿組成。

另一方面,圖6和圖1中,方波的上升時間均為15 ns左右,這說明方波改進算法并沒有導致上升時間的增加。

評論