提高FPGA復位的可靠性 你知道多少

電源電路設計中,對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不 可靠復位的現象,本文例舉了提高復位設計可靠性的幾種方法,也就是采用清除復位信號上的毛刺、異步復位同步釋放、專用全局異步復位/置位資源和采用內部復 位等方法來提高FPGA復位的可靠性。

本文引用地址:http://www.104case.com/article/201612/327199.htm對FPGA芯片而言,在給芯片加電工作前,芯片內部各個節點電位的變化情況均不確定、不可控,而這種 不確定且不可控的情況會使芯片在上電后的工作狀態出現錯誤。因此,在FPGA的設計中,為保證系統能可靠進進入工作狀態,以及避免對FPGA輸出關聯的系 統產生不良影響,FPGA上電后要進行復位,且為了消除電源開關過程中引起的抖動影響,復位信號需在電源穩定后經過一定的延時才能撤銷,FPGA的復位信 號需保證正確、穩定、可靠。

復位設計方法分類

復位的目的是在仿真時將設計強制定位在一 個可知狀態,合理選擇復位方式是電路設計的關鍵。根據與系統時鐘域的關系,復位電路可分為同步復位和異步復位。同步復位是指復位信號只在時鐘沿到來時,才 有效。否則,無法完成對系統的復位工作。異步復位是指無論時鐘沿是否到來,只要復位信號有效,使對系統進行復位。

根據是否存在外部復位端口,復位電路又可分為外部復位和內部復位。外部復位是指復位信號主要來自外部引腳的輸入,如復位按鈕、電源模塊輸出等。內部復位信號則是主要由FPGA內部電路產生。

復位設計方法的比較

(1)同步復位

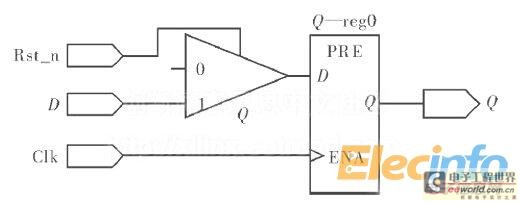

指 定同步復位時,always的敏感表中僅有一個時鐘沿信號,只有當時鐘沿采集到同步復位的有效電平時,才會在時鐘沿到達時刻進行復位操作。若目標器件或可 用庫中的觸發器本身包含同步復位端口,則在實現同步復位電路時可直接調用同步復位端。然而多數目標器件的觸發器本身并不包含同步復位端口,需使復位信號與 輸入信號組成某種組合邏輯,然后將其輸入到寄存器的輸入端。為了提高復位電路的優先級,通常在電路描述時使用帶有優先級的if…else結構,復位電路在 第一個if下描述,其他電路在else或else…if分支中描述。復位電路綜合后的RTL圖如圖1所示。

圖1 同步復位電路圖

根 據同步電路的特點,其電路優點有:同步復位有利于基于周期機制的仿真器進行仿真;使用同步復位可設計100%的同步時序電路,有利于時序分析,其綜合結果 的頻率較高;(3)同步復位僅在時鐘的有效沿生效,可有效避免因毛刺造成的亞穩態和錯誤。毛刺信號是由FPGA內部結構特征決定的,同步復位在進行復位和 釋放復位信號時,僅當時鐘沿采到復位信號電平變化時進行相關操作,若復位信號樹的組合邏輯出現了某種毛刺,此時時鐘沿采到毛刺的概率較低,由此通過時鐘沿 采樣,可有效過波復位電路組合邏輯產生的毛刺,增強了電路穩定性。

同步復位的缺點有:多數目標器件庫的觸發器本身并不包含同步復位端口,使 用同步復位會增加更多邏輯資源;同步復位的最大問題在于必須保證復位信號的有效時間,需要一個脈寬延展器以確保復位信號有一定脈沖寬度,由此才能保證所有 觸發器均能有效復位。由于同步復位僅當時鐘沿采到復位信號時才會進行復位操作,所以其信號的持續時間要大于設計的最長時鐘周期,以保證所有時鐘的有效沿都 能采樣到同步復位信號。事實上,僅保證同步復位信號的持續時間大于最慢的時鐘周期是不夠的,設計中還需考慮到同步復位信號樹通過所有相關組合邏輯路徑時的 延時,以及由于時鐘布線產生的偏斜。只有同步復位大于時鐘最大周期,加上同步信號穿過的組合邏輯路徑延時和時鐘偏斜延時,才能確保同步復位的可靠。

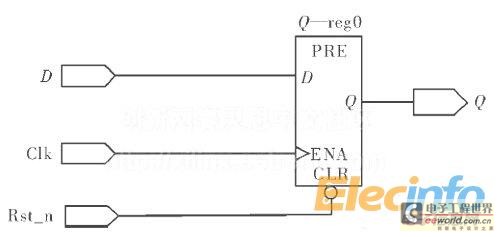

(2)異步復位

指 定異步復位時,只需在always的敏感表中加人復位信號的有效沿即可,當復位信號有效沿到達時,無論時鐘沿是否有效,復位均會立即發揮其功能。大多數目 標器件和ASIC庫的觸發器均包含異步復位端口,異步復位會直接接人觸發器的異步復位端口,綜合后的RTL圖如圖2所示。

圖2 異步復位電路圖

根據異步電路的特點,異步復位的優點有:由于多數目標器件庫的觸發器都包含異步復位端口,異步復位會節約邏輯資源;異步復位設計簡單;對于多數FPGA,均有專用的全局異步復位/置位資源(GSR,GlobalSetReset),還可使用GSR資源,異步復位到達所有寄存器的偏斜最小。

異 步復位的缺點如下:異步復位的作用和釋放與時鐘沿并無直接關系,異步復位生效時問題并不明顯;但當釋放異步復位時,若異步復位信號釋放時間和時鐘的有效沿 到達時間幾乎一致,則容易造成觸發器輸出為亞穩態,形成邏輯錯誤;若異步復位邏輯樹的組合邏輯產生了毛刺,則毛刺的有效沿會使觸發器誤復位,造成邏輯錯 誤。

外部復位,復位信號主要來自外部引腳的輸人。復位信號在電路板上可能會受到來自其他線路的串擾,因此可能產生毛刺,在無需復位系統時, 毛刺信號可能導致系統誤復位。而內部復位,FPGA上電配置完成后,由FPGA內部電路產生復位信號,復位信號與時鐘同步。通常內部復位的設計方法是:設 計一個初始值為0X0000的SRL16,將其輸人接高電平,輸出作為復位信號。復位可靠性設計方法

(1)消除復位信號上的毛刺

在系統設計中,若采用低有效復位信號,可按照圖3所示方法對復位信號中的毛刺進行消除。延時器件對數據進行延時的長度決定復位毛刺消除電路所能避免的毛刺長度,而延時器件的延時長度也決定需要提供有效復位信號的最短時間。

如 果復位信號高有效,則將圖3中的或門改為與門使用。為更好地消除毛刺,可在復位毛刺消除電路后再加上寄存器對復位信號進行時鐘同步。在通常復位電路的設計 中,毛刺的長度一般情況下》1個時鐘周期,《16個時鐘周期。為節省資源,延時器件通常選用SRL16。SRL16可設置初始值,但不帶復位功能 16bit移位寄存器,能夠通過A0~A3的4根地在線選擇從第幾個寄存器輸出。通常將其作為一個普通的16bit移位寄存器使用。

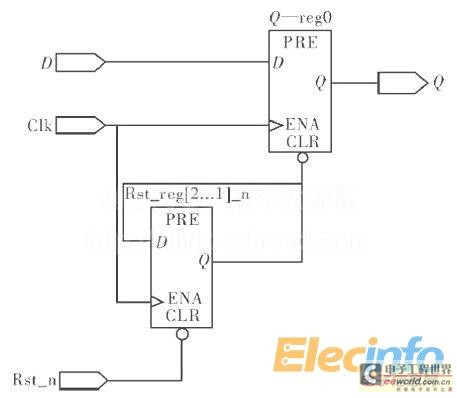

(2)異步復位同步釋放

在 有些應用中,復位信號需要在時鐘尚未給出或不穩定的情況下傳到后級,在時鐘穩定之后,再撤去復位信號。此時需使用異步復位來實現。由于異步復位時,時鐘和 復位關系的不確定性,易造成觸發器輸出亞穩態,引起邏輯錯誤。為確保其復位的可靠性,通常采用異步復位,同步釋放的方式。

所謂異步復位,同步釋放就是在復位信號到達時不受時鐘信號的同步,而是在該信號釋放時受時鐘信號的同步。通過一個復位信號綜合器便可實現異步復位,同步釋放。綜合后的RTL圖如圖3所示,其仿真結果表明該電路能有效的實現復位及脫離復位。

圖3 異步復位、同步釋放電路圖

(3)采用專用全局異步復位/置位資源

全局異步復位/置位資源的主要作用是對系統中存在的所有觸發器、鎖存器、查找表單元的輸出寄存器進行復位,不會占有額外的布線資源。使用GSR資源,異步復位到達所有寄存器的偏斜最小。

(4)采用內部復位的設計方法

在無需復位信號先于時鐘信號產生的應用中,為避免外部復位毛刺的影響、異步復位電路可能引起的亞穩態以及減少資源的使用率,可通過FPGA產生內部復位,然后采用異步的方式對其的內寄存器進行復位。由于該復位信號由FPGA內部產生,不會因外部干擾而產生毛刺,同時又與時鐘同步,不存在因異步復位導致的亞穩態現象,因此可確保系統可靠復位。

評論