一種多通道ADC采樣板系統(tǒng)電路設(shè)計(jì)

ADC板的設(shè)計(jì)從通道上來劃分的話,可以分為單通道ADC板和多通道ADC板,除去有效位數(shù)、動(dòng)態(tài)范圍、最大采樣率以及輸入帶寬等一些基本參數(shù)以外,多通道ADC板相對(duì)于單通道ADC板來說,往往還要衡量通道間幅度一致性和通道間相位一致性,這也正是多通道ADC板設(shè)計(jì)的一個(gè)難點(diǎn)。為了滿足四路ADC之間通道間幅度一致性和通道間相位一致性的指標(biāo)要求,首先需要將四路ADC芯片的采樣時(shí)鐘做到盡可能同步,實(shí)現(xiàn)四路ADC芯片對(duì)輸入中頻信號(hào)的同步采集。為此,本設(shè)計(jì)采取了把外部輸入采樣時(shí)鐘通過同一時(shí)鐘驅(qū)動(dòng)芯片分發(fā)后送給四路ADC芯片作為同步采樣時(shí)鐘的方式,在時(shí)序上保證了四路ADC芯片采樣時(shí)鐘的同步。

本文引用地址:http://www.104case.com/article/201612/327074.htm時(shí)鐘分發(fā)單元電路設(shè)計(jì)

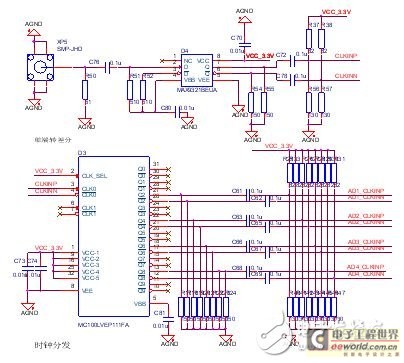

時(shí)鐘分發(fā)單元需要差分時(shí)鐘輸入,而外部輸入時(shí)鐘信號(hào)為單端信號(hào),因此外部時(shí)鐘在進(jìn)入時(shí)鐘分發(fā)單元之前首先需要進(jìn)行單端信號(hào)到差分信號(hào)的轉(zhuǎn)換,此處采用MAX9321BEUA芯片完成了把外部輸入單端時(shí)鐘轉(zhuǎn)變?yōu)椴罘謺r(shí)鐘的功能。時(shí)鐘分發(fā)單元采用MC100LVEP111FA芯片,此芯片為1:10路低偏移差分時(shí)鐘驅(qū)動(dòng)芯片,各引腳之間的輸出到輸出偏移典型值僅為20ps,并且所產(chǎn)生的抖動(dòng)非常小。通過此芯片理論上實(shí)現(xiàn)了四路ADC芯片采樣時(shí)鐘的同步。時(shí)鐘分發(fā)單元的具體原理圖如圖2所示。

圖2 時(shí)鐘分發(fā)單元原理圖

可調(diào)時(shí)鐘延遲單元電路設(shè)計(jì)

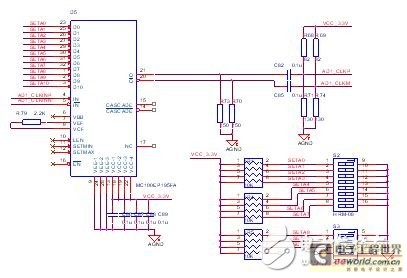

由于芯片制造工藝以及實(shí)際電路板設(shè)計(jì)等各種客觀因素的存在,外部時(shí)鐘實(shí)際到達(dá)四路ADC芯片的時(shí)間相差可能大于理論值,造成了四路ADC采樣時(shí)鐘滿足不了同步的要求,進(jìn)而影響四路ADC芯片間的通道間幅度一致性和通道間相位一致性。為此,在每一路采樣時(shí)鐘到達(dá)ADC芯片之前增加了可調(diào)時(shí)鐘延遲單元。可調(diào)時(shí)鐘延遲單元可以調(diào)節(jié)每一路時(shí)鐘信號(hào)的延遲時(shí)間,修正四路ADC采樣時(shí)鐘之間的相對(duì)延遲,從而實(shí)現(xiàn)了四路ADC采樣時(shí)鐘的同步。其中一路可調(diào)時(shí)鐘延遲單元的原理圖如圖3所示。

圖3 可調(diào)時(shí)鐘延遲單元原理圖

上述可調(diào)時(shí)鐘延遲單元采用了MC100EP195FA芯片,該芯片是可編程延時(shí)單元,可以選擇10ps為延遲時(shí)間單位遞增,最大延遲時(shí)間可達(dá)到 10ns。具體來說就是通過對(duì)此芯片配置不同的D[9:0]值,得到不同的延遲時(shí)間。通過調(diào)節(jié)時(shí)鐘延遲單元可以保證四路ADC采樣時(shí)鐘的同步采集。時(shí)鐘延遲單元部分的延遲時(shí)間配置值。

本文設(shè)計(jì)的四通道ADC已經(jīng)得到成功使用,實(shí)際所測通道間幅度一致性小于0.5dB;通道間相位一致性小于5。ADC的有效位數(shù)為9.8bit,滿足了設(shè)計(jì)的需求。本文提供了一種多通道ADC設(shè)計(jì)的思想,為滿足通道間幅度一致性和通道間相位一致性的要求,需要各通道ADC采樣時(shí)鐘的同步。實(shí)際證明,采用時(shí)鐘延遲單元是一種保持多通道采樣時(shí)鐘同步的簡單易行的方式。

評(píng)論