CMOS低中頻藍牙射頻收發器電路模塊設計

目前正在研發、將來終將成為主流射頻收發器的CMOS射頻電路的體系結構和電路設計,設計實例將展示CMOS射頻電路的良好性能,并預示CMOS射頻集成電路取代砷化鎵和SiGe電路實現系統集成。

本文引用地址:http://www.104case.com/article/201612/327059.htmCMOS射頻收發器原理:傳統的射頻收發電路普遍采用超外差結構,這種成熟的體系結構需要采用二級混頻和片外聲表面濾波器,成本高。正在研發的CMOS低中頻或直接轉換體系結構只需要采用一級混頻,同時能節省片外聲表面濾波器。但是直接轉換的體系結構需要克服直流失調等問題。采用CMOS射頻收發電路的最大優點是可以和基帶處理器(數字電路)及A/D、D/A轉換器(混合信號電路)集成于一個芯片。單片集成的含射頻、基帶及模數、數模轉換電路使電路可靠性好,功耗低和成本低。單片集成CMOS無線通信電路是目前研究熱點,正走上商業化。

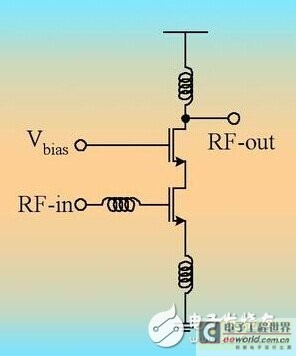

CMOS射頻IC電路:采用直接轉換的CMOS射頻IC主要有低噪聲放大器、混頻電路、功率驅動電路和頻率綜合電路等射頻單元組成。在射頻領域,我們更多注意的是功率傳輸和放大,其中低噪聲放大器的電路圖如圖所示。

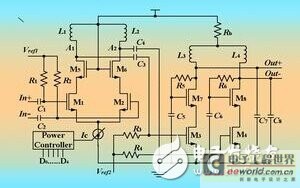

它的核心技術是輸入阻抗匹配和輸出負載的設計,片上電感作為負載可以獲得較高的增益和頻率特性,為了抑制共模電平,差分結構的低噪聲放大器也經常采用。國內已有CMOS混頻器報導采用吉爾布特乘法單元的混頻電路如圖3所示,混頻器的性能主要是線性度,在提高線性度方面,目前有人采用電感負載和共源極電流耦合輸入。功率驅動電路一般會采用二級功率放大的電路,為了滿足不同射頻系統的需要和保證輸出功率,功率驅動電路需要考慮增益控制電路和封裝、連線及引腳的分布參數。為了得到低噪聲時鐘和低相位噪聲的正交信號,采用片上電感和變容二極管的LC信頻壓控器及二分頻正交信號產生器是一種好的選擇。

采用倍頻VCO可以減少射頻信號對VCO的牽引和VCO對信號的泄漏。Sigma-Delta分數分頻能夠進一步降低VCO的相位噪聲。低中頻(2MHz中心頻率)體系結構和直接轉換的藍牙、無線局域網和WCDMA射頻電路。圖6是單片集成的CMOS射頻收發電路芯片照片,芯片左上角是正交時鐘產生電路,右下角是功率放大電路,右上角是復數濾波器。在深亞微米CMOS工藝線流片后,對各功能塊進行測試,電路達到了設計的要求,能夠滿足藍牙接收芯片必須的功耗和性能。

評論