關于JESD204B轉換器與FPGA匹配的設計關鍵點

發器頻率間隙。

本文引用地址:http://www.104case.com/article/201612/326843.htm

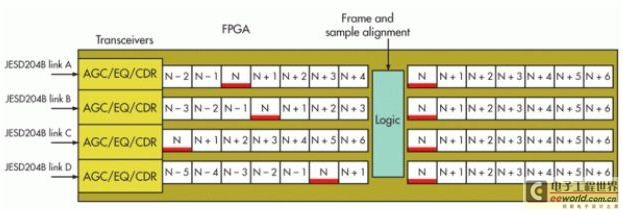

圖4.JESD204B協議中規定,對齊來自于多個ADC、具有不同延遲的采樣數據從而在FPGA中實現同步。來自多個鏈路的幀數據或標記的樣本可針對同步處理進行重對齊。

小結

新型轉換器與JESD204B之類的FPGA接口較為復雜,使其顯得難于處理,此時分解關鍵系統需求至關重要。必須了解采樣速率和JESD204B通道速率倍頻器。根據IP支持、收發器數、收發器速度和頻率間隙等因素來進行規劃和選擇合適的FGPA產品,有助于正確選擇轉換器。通過重點關注一些與FPGA相匹配的高級標準,可簡化選擇合適的JESD204B轉換器的過程。

評論