巧用DC/DC轉換器以滿足FPGA電源設計需求

利用FPGA或CPLD進行電路設計的流程由以下幾個普通步驟組成:設計入口、設計確認、設計匯編和器件編程。設計入口階段由捕獲設計組成,不是通過利用電腦輔助設計工具創建圖形化原理圖,就是通過利用Verilog或VHDL等硬件描述語言來描述電路。在捕獲設計之后,通過使用電路模擬來檢驗正確的功能性和性能加以驗證。如果電路沒有達到要求性能,則工程師師就回到設計入口階段對設計加以調整,然后重復設計驗證階段。設計入口和設計驗證步驟可能反復多次,才能使設計能夠滿足全部功能和性能要求。在獲得令人滿意的設計之后,工程師使用FPGA或CPLD器件供應商提供的軟件對設計進行“匯編”,用于對實現設計的器件進行配置。編譯形成的文檔被下載到FPGA或CPLD,并給內部邏輯器件編程使之具有正確的功能性。

為現場可編程器件供電

通常利用三個基本電源軌對FPGA供電:核心電源軌、I/O電源軌和輔助電源軌。其中每個電源軌都具有不同的負載電源要求。核心電源軌VCCINT,向器件的內部邏輯供電,通常具有最嚴格的電流要求。對上幾代的FPGA,VCCINT上面的電壓可能高達3.3V,而目前的器件則低至1.2V。I/O電源軌VCCIO為FPGA的輸入/輸出模塊供電。該電源軌上的電壓可能是1.5V、1.8V、2.5V或3.3V,取決于所采用的I/O標準。具體選擇什么I/O標準,受FPGA將與之通訊的器件左右。輔助電源軌VCCAUX用于為FPGA上面的數字時鐘管理器和JTAG I/O供電,電壓通常是2.5V或3.3V。

可變的功率要求

通過重復上述的設計匯編和下載步驟,工程師可以隨時改變FPGA或CPLD的編程和配置。FPGA根據新設計的要求進行重新配置沒有次數限制。不需改變電路板上的線跡、不需要更換元件、不需要重新焊接,因此可以非常迅速及方便地解決故障和進行調整。另外,可以為給定的設計添加功能和特點,而對于物理設計并無影響。這使現場可編程器件獲得巨大優勢,可以作為復雜的數字系統的實現手段。

但是,獲得這樣的靈活性也需要付出代價。FPGA的電源要求,具體而言就是它要消耗的電源電流,與設計的復雜程度成正比。對FPGA進行重新配置,使其具有新的功能,將改變對為其供電的電源系統的要求。FPGA被使用的程度越高,它需要的電流就越大。電流需求也會隨著時鐘頻率的上升而增加,因此FPGA速度越快,它消耗的功率越大。因此,FPGA功能的改變將決定電源設計的改變。

單片雙通道降壓轉換器

為了滿足對于緊湊和靈活的電源系統的需求,以及為數字設計者提供可以迅速設計和重新配置FPGA電源的解決方案,Intersil推出了ISL65426。ISL65426是一種具有雙路輸出的單片同步降壓轉換器,能夠提供高達6A的總體負載電流,效率高達95%。兩個輸出電壓是邏輯可調節的,或者是電阻可調節的,用戶可對每個輸出通道的負載電流進行配置。因此,如果FPGA/CPLD功率需求在設計過程中發生變化,只需為每個通道重新指定負載電流就能滿足新的要求。

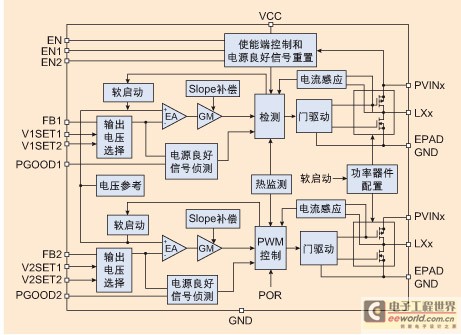

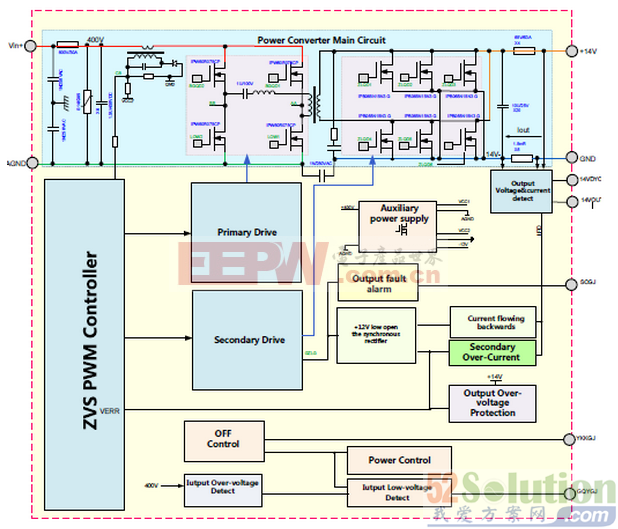

這種完全集成的同步降壓DC/DC轉換器消除了選擇功率MOSFET、確定環路補償參數等方面的工程工作,并簡化了電感和電容的選擇過程。總體元件數量減少,因為內部高階MOSFET是利用PMOS器件實現的,而不是典型的NMOS器件,從而不需要自舉電容。內部數字軟啟動能力和內部環路補償消除了外部軟啟動電容器和外部RC補償網絡。熱增強型QFN封裝,1.1MHz的高工作頻率和BOM元件數量減少,成就了面向FPGA和VCCINT和VCCIO電源軌的緊湊型電源解決方案(圖1)。

圖1:ISL65426的功能性結構圖

可配置負載電流能力

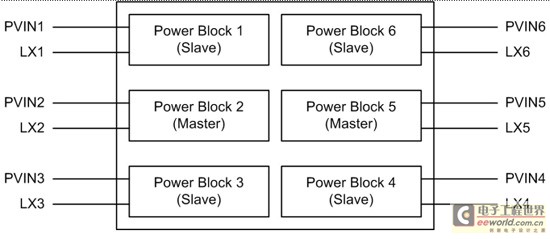

ISL65426使用了由用戶可配置電源模塊組成的獨特架構,有利于快速設計電源系統。該電源模塊架構允許劃分六個1A模塊劃,具有四種電源配置選擇。每個同步轉換器通道與一個主電源模塊相配。剩余的四個電源模塊是從屬模塊,用戶可以把它們分配給任何一個主轉換器通道,如圖2所示。

圖2:ISL65426電源模塊架構

利用這些電源模塊,可以指定ISL65426的每個通道的負載電流能力。芯片包含兩個邏輯引腳,即ISET1和ISET2,根據下表為每個通道安排負載電流分配:

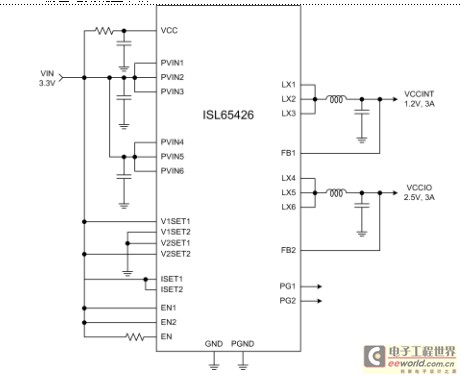

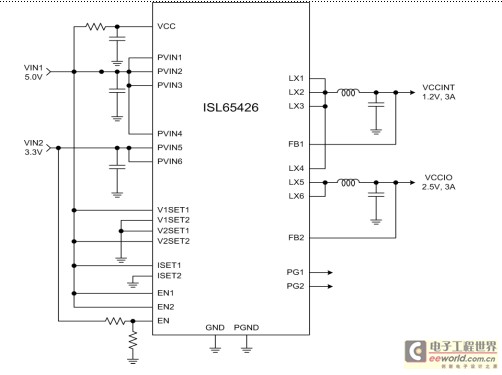

每個電源模塊都有自己的電源連接――PVIN,以及電感連接――LX。ISL65426可以用來調節來自一個或兩個輸入電源的輸出電壓。隨著給定電源設計對負載電流的要求發生變化,可以以最小的努力來重新調整設計。因為ISL65426包含內部電源開關,而且是內部補償,因此通道之間的負載電流分配的變化通過改變ISET1和ISET2的邏輯電平,以及到芯片的PVIN和LX連接就能實現。圖3和圖4所示為一些典型的配置。

圖3:單電源3A/3A輸出電流配置中的ISL65426

圖4:單電源4A/2A輸出電流配置中的ISL65426

靈活的輸出電壓選擇

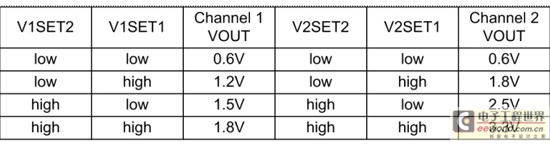

ISL65426能夠在不使用外部反饋電阻的情況下規劃每個通道的輸出電壓。V1SET1、V1SET2、V2SET1和V2SET2等四個邏輯引腳從一個通用值清單中為每個通道選擇輸出電壓。實質上是一個2位VID輸入,為重新設計和重定目標提供了進一步的便利,因為它允許通過邏輯,而不是通過對電源板及其元件進行物理改變來調整輸出電壓,從而可以迅速和可靠地實現改變。另外,這個2位VID輸入允許對這些系統中的ISL65426轉換器通道的輸出電壓進行數字化控制,而且在這些系統中需要這樣的控制。表1列出了輸出電壓選擇。

表1:輸出電流配置

表2:輸出電壓配置

不必使用反饋電阻,簡化了設計,減少了元件數量并提高了系統的總體精度。但這種輸出電壓選擇的方便性并未犧牲設計靈活性,因為ISL65426保留了設置輸出電壓的傳統電阻分壓器方法。芯片的內部基準電壓是0.6V,在使用5V的輸出電源時,通過電阻反饋可以把每個通道的輸出電壓設定在0.6?V之間的任意值。

集成故障保護

ISL65426具備過壓、欠壓、過流和過溫保護機制,以便把全部故障監控和保護功能都完全集成到一個芯片之中,而且不需要使用外部元件。在過壓情況下(輸出電壓高于過壓水平――基準電壓的115%),ISL65426將主動地努力調節輸出電壓,使之下降到規定值。在欠壓保護情況下,對反饋電壓進行監控,并與欠壓水平(基準電壓的85%)進行比較。如果在一個轉換器通道上檢測到欠壓情形,則一個4位計數器就累加一次。如果在同一個開關周期中探測到兩個轉換器通道都出現了欠壓情形,則該4位計數器就累加兩次。每當轉換器通道上探測到欠壓情形,這個計數器就繼續累加。一旦計數器溢出,欠壓保護邏輯就把兩個轉換器都切斷。

過流保護電路也采用了一個4位計數器記錄過流事件。對每個電源模塊中的電流進行測量并與和所用的具體電源模塊配置相適應的過流水平加以比較。如果測得的電流超過了過流閾值,一個4位加/減計數器就加1。如果測得的電流在計數器溢出之前降至過流閾值下方,則計數器重置。如果兩個轉換器通道都在同一開關周期內出現過流現象,則計數器就加2。一旦計數器溢出,兩個轉換器通道就被切斷。如果在同一個周期中測得的兩個轉換器通道的電流都降至了過流水平的下方,則計數器重置。

最后,在過溫保護方面,一個內部溫度傳感器連續監控ISL65426的節溫,如果溫度超過150°C,傳感器就命令ISL65426關閉兩個傳感器通道和栓鎖(latch off)。

電壓監控與電源時序控制

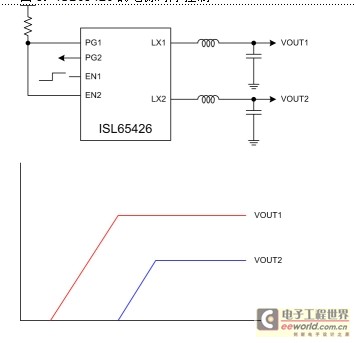

ISL65426的每個轉換器通道都具有自己的使能信號和電源良好信號(power-good signal)。這樣就可以實現對每個輸出電壓的單獨控制和監控,使電壓追蹤和電源時序監控成為可能。有兩個使能信號――EN1和EN2,用于啟用或禁用每個通道。還有一個系統使能信號EN,可以用于同時啟動或關閉兩個通道。當接收到使能信號而且通道被啟用時,一個數字軟啟動功能通過以20ms的固定間隔來逐漸提高基準電壓來提升輸出電壓。對于電壓監控,每個轉換器通道都有自己的電源良好信號,當某個通道的輸出電壓超出調節限度時可以被確定。對于ISL65426的兩個輸出電壓的時序測定是通過把一個通道的電源良好信號連接到另一個通道的使能輸入來實現的。在這個配置中,第二個輸出當第一個輸出處于調節過程中時不會開始軟啟動周期,如圖5所示。

圖5:ISL65426的電源時序控制

完整的FPGA電源解決方案

由于配置方便、具有集成的電源器件、效率高、具有集成的故障監控和保護、支持使用陶瓷電容器和RoHS兼容,ISL65426代表一種完整的和環境友好的電源解決方案。在總體FPGA或CPLD系統實施過程中,可以快速、方便及可靠地實施設計變化,從而可以縮短設計周期和減少設計反復。

評論