基于FPGA的多普勒測振計信號采集系統的設計方案

1 系統總體結構

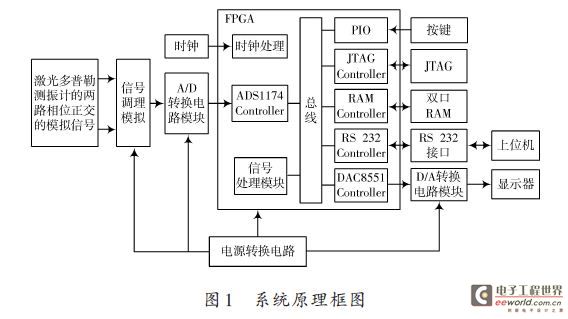

本文引用地址:http://www.104case.com/article/201612/326198.htm激光多普勒測振計信號采集與處理系統要求既要具有高速實時的采集和處理能力,也要具有豐富的外部接口,同時,考慮到系統穩定性和靈活性的要求,采用核心板和底層板結合的硬件結構。系統原理框圖如圖1所示,FPGA 芯片采用Atera 公司的Cyclone Ⅱ 系列EP2C5Q208C8N,它采用90 nm 工藝,具有4 608個邏輯單元。此外,系統還包括信號調理模塊、A/D轉換電路模塊、D/A 轉換電路模塊和外部接口單元等部分組成。

系統采用±15 V 電源供電,選用多塊電壓轉換芯片,提供5 V,1.8 V,3.3 V和1.2 V電壓。

2 信號采集和處理系統設計

2.1 硬件電路設計

激光多普勒測振計信號采集與處理系統采用核心板和底層板結合的硬件結構,核心板主要包括FPGA芯片、串行配置芯片(EPCS)、聯合測試調試接口(JTAG),其通過108個引腳插針與底層板插座一一對應連接。

底層板電路主要包括電源轉換電路、信號調理電路、A/D轉換電路、D/A轉換電路和串行通信轉換電路。

電源轉換電路通過7805 穩壓芯片、AMS1117 穩壓芯片和LM1085穩壓芯片實現電源電壓的轉換,為系統提供5 V,1.8 V,3.3 V 和1.2 V 電壓。信號調理電路模塊包括兩路差分放大電路,每路差分放大電路由一片高性能的全差分音頻運算放大器芯片OPA1632 構成。A/D 轉換電路模塊是在四通道16 位求和型模數轉換芯片ADS1174、穩壓芯片REF1004 以及集成運放芯片OPA350的基礎上實現的,高速狀態下,ADS1174芯片速度可以達到52 KSPS,并支持多通道并行處理。采用DAC8551 和REF02 穩壓芯片實現D/A 轉換,DAC8551是一款16 位電壓輸出模數轉換芯片,REF02 穩壓芯片為DA芯片提供2.5 V的參考電壓。由于RS 232在通信領域的廣泛應用,本文設計系統采用RS 232 串行方式進行通信,考慮到激光多普勒測振計信號采集與處理系統中FPGA 接口電路是TTL 電平,所以需要經過MAX3232芯片實現與RS 232標準電平的轉換。硬件電路板如圖2所示。

2.2 FPGA邏輯設計

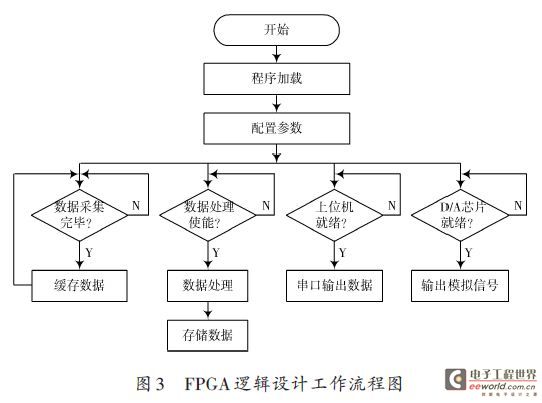

在FPGA邏輯設計中,采用ALTEra公司的QUARTus Ⅱ綜合開發環境對FPGA進行設計、仿真和調試,實現信號的采集和處理功能,FPGA邏輯設計工作流程圖如圖3所示。

在工作過程中,FPGA首先檢測是否接收到數據采集完畢的使能信號,如果沒有接收到就一直進行檢測,如果收到就讀取16 位數據并緩存。當FIFO 接近全滿狀態時啟動數據處理邏輯,數據處理邏輯通過一系列乘加運算結合流水線的設計方法實現,并將運算結果適當截位輸出給雙口RAM.雙口RAM 擁有兩套完全獨立的數據線、地址線和讀寫控制線,當檢測到有數據輸入時,讀地址開始加1,否則讀地址保持不變。上位機準備就緒,即雙口RAM 數據準備輸出時,雙口RAM 寫地址開始加1,通過串行接口將數據輸出。在輸出模擬信號時,只有當DAC8551芯片輸入寄存器接收到24位數據,同時同步信號為低電平時,才能啟動D/A轉換邏輯。下面將介紹幾個典型數字邏輯模塊的關鍵設計點。

(1)時鐘模塊

本設計中外部晶振提供給FPGA的時鐘為50 MHz,時鐘模塊的功能就是根據設計要求,利用鎖相環以及使能時鐘的設計方法為各個模塊提供所需的時鐘信號。通過鎖相環配置工具將50 MHz的系統時鐘進行1/2分頻,從而產生頻率為25 MHz并滿足時序約束的主時鐘。使能時鐘設計,即不增加新的時鐘,而只是利用原有主時鐘,讓分頻信號作為使能信號來使用,通過該設計對主時鐘進行1/16分頻,為信號處理模塊提供工作時鐘。

(2)A/D邏輯模塊

A/D 邏輯模塊的任務是根據ADS1174 的轉換時序圖,在芯片的引腳發出或接收相應的信號,使得ADS1174完成啟動、配置和數據讀取操作。其控制操作如下:首先配置ADS1174 的相關參數,包括運行模式、接口類型等,然后通過查詢ADS1174的DRDY信號來判定數據轉換是否完成,開始讀取數據,最后將讀得數據進行串并轉換,同時完成數據的緩存。A/D邏輯模塊每完成一次信號采樣,則等待下一次觸發脈沖的到來。

(3)數據處理模塊

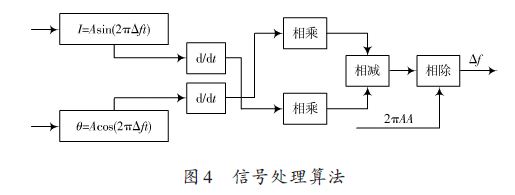

數據處理模塊的功能是提取出多普勒測振計信號中的頻移信號,本設計采用如圖4 所示的信號處理算法,通過微分和乘加運算,同時結合流水線的設計方法來實現。微分運算的處理是將前一個數據延遲一個單位時間,用當前的數據減去前一個數據得到的。通過宏模塊構建16 b × 16 b有符號乘法器來實現乘法運算,同時為了避免溢出,對乘法運算結果適當截位。相關除法器操作則與乘法器類似。

(4)雙口RAM模塊

本文設計中雙口RAM 用于存儲經過處理的數據,一方面通過RS 232 接口提供給上位機操作,另一方面通過DAC8551轉換成模擬信號。雙口RAM擁有兩套完全獨立的數據線、地址線和讀寫控制線,并允許兩個獨立的系統或設備同時對其進行隨機性訪問。該雙口RAM 模塊是通過調用Quartus Ⅱ自帶的參數化模型庫實現的,容量為4 KB.

(5)數據通信模塊

RS 232采用的是異步通信協議,基本的異步通信只需包括通信發送端和通信接收端兩根信號線。該模塊由三個子模塊組成:波特率發送器模塊、數據發送模塊、數據接收模塊。波特率發生器模塊主要用于產生接收模塊和發送模塊的時鐘頻率,其實質是一個分頻器,數據接收模塊的作用就是將接收到的串行數據轉換成并行數據并輸出,數據發送模塊的作用相當于一個移位寄存器,其功能就是按照一定的波特率將移位寄存器中的數據一位一位移出。數據收發過程是通過狀態機實現的,設計中波特率發生器模塊的輸出時鐘為實際串口數據波特率的16倍,當輸入線路邏輯發生跳變時,開啟采樣計數器,當計數器計數到起始位數據中間時刻時即可認定接收到的數據是起始位數據,依次類推,只有計數器計數到每個數據的中間位置時才開始采集該數據。

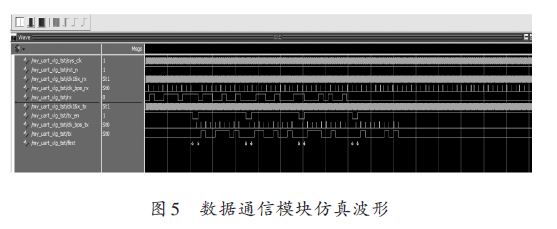

3 仿真驗證

激光多普勒測振計信號采集與處理系統采用MentorGraphICs公司Modelsim軟件進行仿真驗證。數據通信模塊仿真波形如圖5所示。其中,first發生跳變會引起數據發送使能信號的翻轉,從而給UART傳輸系統中數據發送模塊一個使能信號。clk16x_rx,clk16x_tx是由波特率發送器產生的16倍于系統時鐘的信號,分別作用于數據接收模塊和數據發送模塊。按照時間順序由低字節到高字節發送一幀數據0,1,0,0,1,1,1,0,1,1,當數據發送使能信號低電平有效時,被采樣的數據經由數據發送模塊發送出來。由此證明數據通信模塊能夠正常工作。

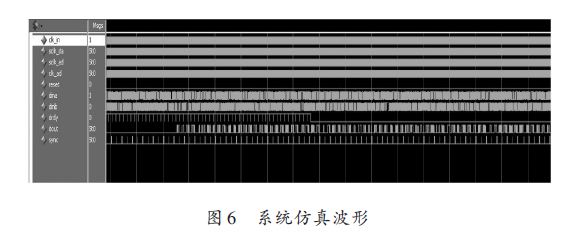

系統仿真波形如圖6 所示。dina,dinb 是由計算機隨機產生的兩路多普勒正交信號,經過ADS1174 模數轉換輸出給FPGA,經過信號處理模塊、雙口RAM 模塊以及DA控制模塊,從dout口輸出給DAC8551芯片進行數模轉換。

4 結語

基于激光多普勒測振技術的聲光耦合系統是光聲淺海地形遙感系統的重要組成部分,包括激光多普勒測振系統、水面反射光自適應跟蹤系統以及可調水平平臺三個部分。傳統的淺海地形測量以船只為平臺,采用聲納技術進行,這種測量方法對于一些船只難以駛入的區域便形成了測量盲區,而機載平臺與光聲淺海測量技術的結合克服了這一缺點,大大提高了測量區域的范圍。

測試表明該設計方案能夠保證設計要求的采樣速度和精度,對于信號的實時解調和處理具有實際應用價值。

評論