LED智能照明系統電路模塊設計

隧道照明中心控制器硬件設計

本文引用地址:http://www.104case.com/article/201612/325460.htm硬件設計的任務是根據系統的設計要求,在所選定的微處理器芯片和其他元器件的基礎上,設計出系統的電路原理圖,還包括結構設計、印制板設計等。在設計完成后進行試驗,以便對其不合理的部分進行修正,并最終確定硬件設計方案和完成印制電路板。中心控制器電路主要包括以下幾個部分:(1) 電路核心部分:ARM微處理器、復位電路、晶振電路和電源電路。(2)JTAG電路:實現程序下載與在線調試。(3) 外圍電路:CAN總線通信電路、USB接口、存儲電路、LCD液晶顯示、鍵盤電路、串行通訊電路。

核心電路設計

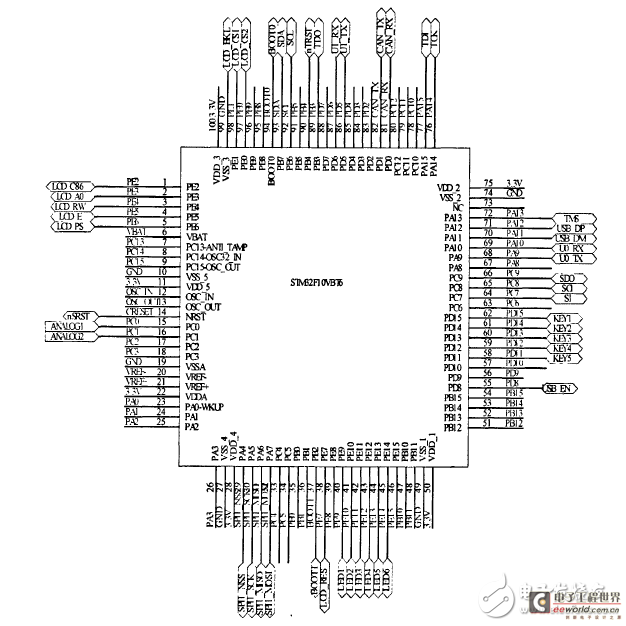

中心控制器的微處理器引腳圖如圖3.2所示,它主要包括芯片中所使用的各個接口的網絡標號及與外圍電路的連接方式。

圖3.2STM32F103VBT6引腳圖

電源電路設計

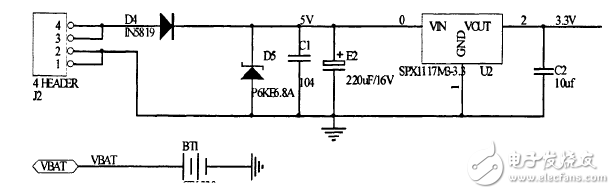

電源電路如圖3.3所示。

圖3.3中心控制器電源電路

STM32的工作電壓為2.0V.3.6V,通過內置的電壓調節器提供所需的1.8V電源。當主電源掉電后,通過VBAT腳為實時時鐘(RTC)和備份寄存器提供電源。5v電源通過J2端口接入電路,并通過SPXlll7M3.3.3將電源穩壓至3.3V。VDDA與VSSA必須分別連到VDD與VSS,這是為了降低噪聲和出錯幾率。SPXI 1l 7M3.3.3輸出電流可達800mA,輸出電壓的精度在正負百分之一之間,具有電流限制和熱保護功能。P6KE6.8A為瞬態抑制二極管,它有效地保護電子線路中的精密元器件,免受各種浪涌脈沖的損壞。電源不僅是核心電路的供電電源,而且還要負責給其他外圍電路供電,電源和地之間的電容是用來去耦的,它提高了系統的抗干擾性。

復位電路設計

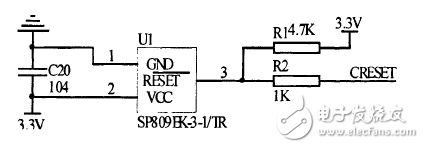

STM32F103VBT6支持三種復位形式,分別為系統復位、上電復位和備份區域復位。除了時鐘控制寄存器RCC CSR寄存器中的復位標志位和備份區域中的寄存器以外,系統復位將復位所有寄存器至它們的復位狀態。外部復位電路如圖3.4所示。

圖3-4中心控制器復位電路

SP809EK.3.1/TR為單功能復位監控器件。當系統上電或電源電壓跌落至閾值電壓,SP809的復位信號RESET就會產生140ms的復位脈沖,保證系統可靠有效的復位。它的輸出典型值為上拉低電平,因此要在RESET--與“電源電壓之間加一個上拉電阻Rl。此電路為外部復位,CRESET連接至lJSTM32F103VBT6的NRST引腳上.低電平有效。

語音識別被認定是未來物聯網領域的基礎需求之一,甚至將會無處不在,詳情請點擊進入》》》

晶振電路設計

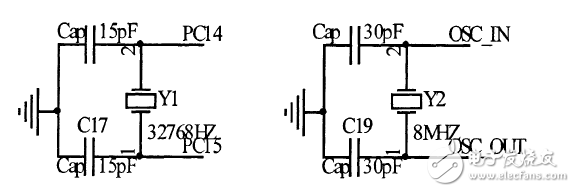

在STM32中,三種不同的時鐘源可被用來驅動系統時鐘(SYSCLK):HSI振蕩器時鐘、HSE振蕩器時鐘和PLL時鐘。高速外部時鐘信號(HSE)由以下兩種時鐘源產生:HSE外部晶體/陶瓷諧振器和HSE用戶外部時鐘。HSI時鐘信號由內部8MHz的RC振蕩器產生,可直接作為系統時鐘或在2分頻之后作為PLL輸入。LSE(低速外部時鐘信號)晶體是一個32.768KHz的低速外部晶體或陶瓷諧振器。晶振電路如圖3.5所示。

圖3.5中心控制器晶振電路

左圖為LSE時鐘,它采用32.768kHz夕b部晶振,為實時時鐘(RTC)提供一個低功耗且精確的時鐘源。LSE晶體通過在備份域控制寄存器里的LSEON位啟動和關閉。右圖為HSE時鐘,采用8MHz夕b部晶振,負載電容值根據所選晶振選取,為系統提供更為精確的主時鐘。為了減少時鐘輸出的失真和縮短啟動穩定時間,晶體和負載電容必須盡可能地靠近振蕩器引腳。

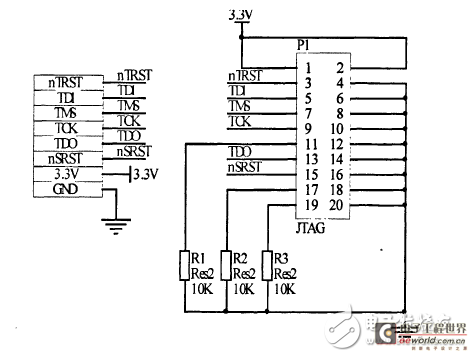

JTAG電路設計

JTAG是一種國際標準測試協議(IEEEl 149.1兼容),主要用于芯片內部測試。現在多數高級器件都支持JTAG協議。JTAG g路如圖3.6所示,這里使用的是20針JTAG接口。各引腳名稱及功能如下:1腳為VTrefH標板參考電壓,接電源;2腳為VCC電源;3腳為nTRST‘狽0試系統復位信號;5腳為TDI鋇IJ試數據串行輸入;7腳為TMS、狽IJ試模式選擇;9腳為TCK測試時鐘:1 1腳為RTCK測試時鐘返回信號,不使用時可以直接接地;1 3腳為TDO測試數據串行輸出;15腳為nSRSTg[標系統復位信號,與目標板上的系統復位信號(NRST)相連,;4、6、8、10、12、14、16、18、20腳為GND接地;17、19腳未定義。

圖3.6中心控制器JTAG電路

為了避免任何未受控制的I/O電平,STM32F103VBT6;(EJTAG輸入腳上嵌入了內部上拉和下拉。JINTRST(PB4)內部上拉,JTDI(PAl5)內部上拉,JTMS(PAl3)內部上拉,JTCK(PAl4)內部下拉。(JTAG IEEE標準建議對TDI、TMS和nTRST上拉,而對TCK沒有特別建議,但在STM32F 1 03VBT6中,JTCK引腳帶有下拉)。

R1、R2、R3均為下拉電阻,令系統復位以后,STM321為部JTAG接口使能,JTAG就可仿真調試。ARM通過JTAG電路與主機的并口連接,先下載程序到FLASHI勾再在器件內通過軟件控制程序的運行,由JTAG接口讀取片內信息供調試使用的方法進行開發。這種方式不需要仿真器和編程器,大大縮短了開發周期,降低了開發成本。

外圍電路設計

STM32具有先進的內核結構和優秀的功耗控制,并且具有性能出眾的片上外設。其USB接口可達12Mbit/s,USART接口高達4.5Mbit/s。它采用基于ARMv7.M體系結構的32位標準處理器Cortex.M3,是專門為微控制系統、工業控制系統和無線網絡系統等功耗和成本敏感的嵌入式應用領域實現高系統性能設計的。

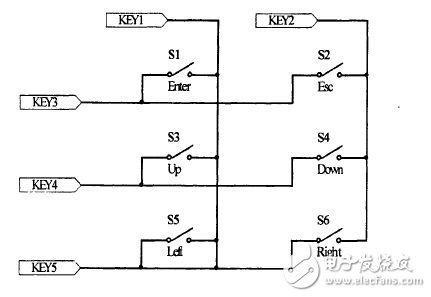

鍵盤電路設計

圖3.7中心控制器鍵盤電路

本部分采用簡單的矩陣式鍵盤設計,電路如圖3.7所示,這樣不僅減少I/O UI的占用,而且便于以后的擴展。這里采用行掃描法,進行按鍵識別。首先,判斷鍵盤中有無鍵按下:將全部行線(KEY3、KEY4、KEY5)置低,然后檢測列線(KEYl、KEY2)的狀態。

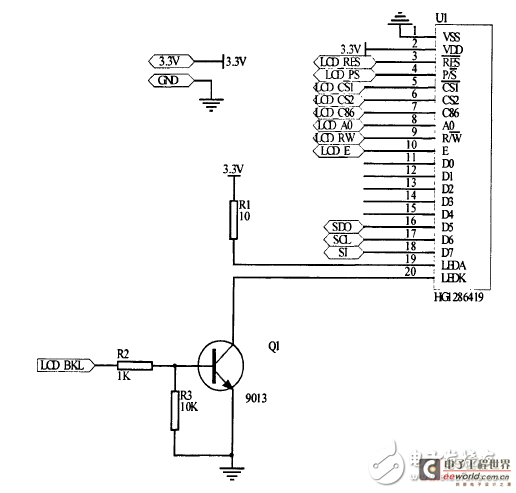

人機界面接口

本系統中的LCD顯示模塊主要用于中心控制器脫離上位機獨立工作時的命令發送與處理。選用清達光電技術有限公司的HGl286419-SYH.LSV型號的圖形點陣液晶顯示模組,它支持串行和并行兩種接口,點陣數為128“64,內置芯片為EPL651 32,可方便的與各種微處理器相連接。

圖3.8中心控制器液晶顯示電路

LCD模塊的接口電路如圖3.8所示。其工作電壓為3.3V,與STM32SE作電壓相同,因此可以直接使用電源電路的輸出電壓,無需額外電源電路設計。它的顯示像素為藍黑色,顯示背景為黃綠色。采用模擬串行通信與ARM芯片連接,連接引腳為SDO(串行數據輸出)、SCL(串行時鐘)、SI(串行數據輸入)分別接蛩jSTM32上的PC9、PC8、PC7引腳上。LCD RES為復位信號,低電平有效。LCD PS用來選擇數據傳輸接口,高電平為并行接口,低電平串行接口。LCD CSl和LCD CS2為片選信號。LCD C86用來選擇時序,高電平為6800時序,低電平為8080日‘-j序。LCD A0用來發送數據還是命令,高電平為數據,低電平為命令。LCD RW用來選擇讀寫信號,當為6800時序時,高電平為讀信號,低電平為寫信號,當為8080Bt序時為寫信號。LCD E為6800時序的使能信號或8080時序的讀信號。LEDA腳和LEDK腳為LED背光源輸入,LEDA接3.3V,LEDK應接地。此處由LCD BKL控制晶體管導通.然后控帶rJLEDK的電平。

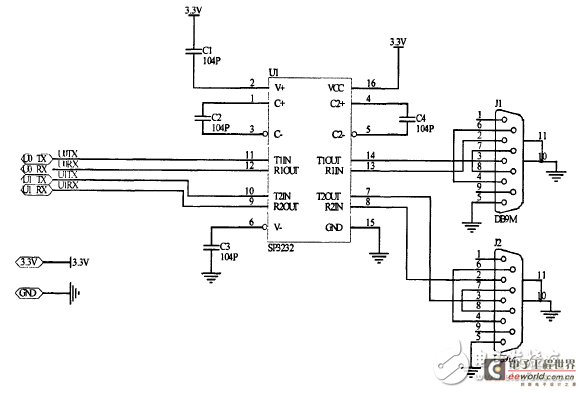

RS232串行接口電路

本系統采用的是標準的DB.9接口,電路如圖3.9所示。由于RS.232.C標準采用負邏輯方式,與STM32F103VBT6的LVTTL電路所定義的高低電平信號完全不同,所以要用SP3232進行RS232電平轉換,SP3232的工作電壓為+3.0¨5.OV,將EIA/TIA.232電平轉換為TTl或CMOS電平。這里有兩路串行通信接口,U0和U1。

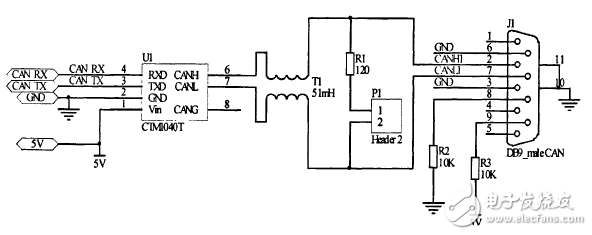

CAN總線通信電路

圖3.10中心控制器CAN通信電路

CAN總線通信電路如圖3.10所示。由于系統中心控制器要與節點控制器進行通信,因此硬件部分包括CAN通信模塊設計,采用CTMl040T是一款帶隔離的高速CAN收發器芯片,該芯片內部集成了所有必需的CAN隔離及CAN收、發器件。該芯片的主要功能是將CAN控制器的邏輯電平轉換為CAN總線的差分電平并且具有DC2500V的隔離功能及ESD保護作用。T1為高頻扼流圈,因為隧道里環境復雜,高頻扼流圈可以濾除高頻干擾,使電路穩定。

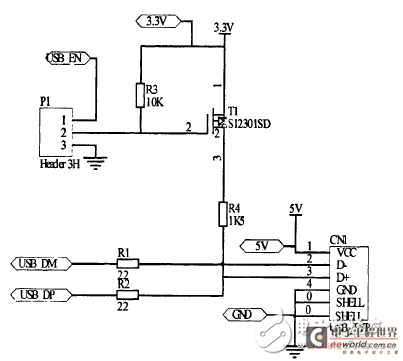

USB接口電路

圖3.1 1中心控制器USB接口電路

USB且P串行通用總線,通常使用一個4針插頭作為標準插頭,其電路設計如圖3.1l所示。USB的D+與D.是差分輸入線,使用的3.3V電壓。而電源與地線可向設備提供5V電壓,最大電流為500mA。USB—EN用于控制是否使能USB通信功能,控制D+和D.的電平。

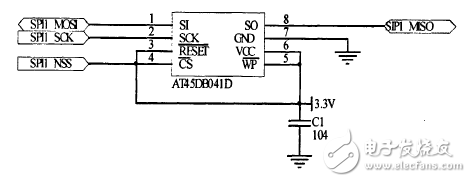

數據存儲電路

由于隧道照明需要存儲操作記錄,包括調光值、操作時間、操作組別等信息,因此使用AT45DB041D存儲數據,電路如圖3.12所示。它通過SPI總線與ARM處理器通信,在需要的時候可以通過上位機發送命令讀取歷史記錄,并且歷史記錄存儲會自動定期清除。CS為芯片選擇引腳,CS腳由高到低的電平轉換時開始對芯片進行操作,反之,由低到高時結束操作。SCK是串行時鐘,SO是串行數據輸出,SI是串行數據輸入。WP是寫保護,WP引腳已經內置上拉,在不使用時,將它接到高電平上。RESET是復位,只要RESET恢復到低電平即可對芯片進行正常操作,芯片內部已經內置了上電復位電路,不使用此引腳時將它接到高電平上。

系統主要包括上位機監控中心、檢測設備、中心控制器、節點控制器和LED驅動電源。通過檢測設備采集數據,然后傳遞給上位機監控中心,上位機進行數據處理之后,向中心控制器發送命令,中心控制器以廣播形式向節點控制器發送命令,通過調節LED驅動電源的輸入電壓控制LED燈的亮度。中心控制器與節點控制器采用CAN總線通信,中心控制器與上位機采用串口通信。

制定了中心控制器、節點控制器與上位機之間的通信協議,并對中心控制器和節點控制器進行了硬件電路設計,主要包括微處理器的選型、通信模塊設計、DA轉換電路設計、液晶顯示設計、數據存儲模塊設計、放大電路設計,并給出了部分電路的詳細原理圖。

評論