針對微控制器應用的采用FPGA的嵌入式應用

導航系統采用微控制器調整系統的圖像顯示器,根據微控制器的輸入提高或降低分辨率。

圖3中的設計展示了一個片上系統的實現,包括微控制器、外圍總線和幾種外設功能,以及用于顯示寄存器文檔、暫存存儲器、調用棧、程序計數器、標記和跟蹤列表的硬件跟蹤調試器。同時還支持微控制器的單步、多步和斷點功能。

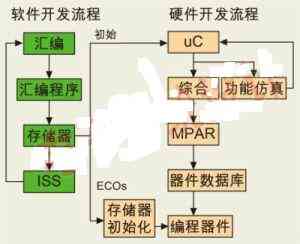

片上系統的例子可用來說明設計工具流程和實現(圖4)。

圖4:片上系統的軟件開發流程及硬件開發流程

微控制器工具和實現

FPGA微控制器的高效率和緊湊實現使得2280 LUT MachXO器件可用于說明圖3中片上系統的設計。

啟動該設計的最簡單方法是參考“快速啟動指南”或項目向導一步一步地設計FPGA。一旦設計項目創建好,下一步就是編寫微控制器程序。C或匯編語言是目前最流行的MCU編程語言。圖5顯示了用匯編語言編寫的I2C Slave程序塊。

圖5:匯編代碼實例

必須對微控制器的每個單元進行分析以決定要執行的操作。如代碼實例所示,I2C寫循環具有5種操作:讀狀態、寫器件地址、寫數據、寫字地址及返回。請注意代碼都加上了注釋。

雖然匯編語言的規范在各種MCU上大多是一致的,但設計者還是應該查閱供應商的MCU指令集文檔,以了解哪些操作是得到支持的。將匯編源代碼轉換到ROM初始化文件的匯編程序是由命令行驅動的,和指令集仿真器一樣,這可以通過匯編器供應商工具套件獲得或者從網上下載。其中有些工具是作為開放源代碼工具提供。例如,LatticeMico8微控制器IP(知識產權)就是作為開放源代碼提供,這是實現嵌入式微控制器的一種獨特有效途徑,可使用戶擁有最大的靈活性。

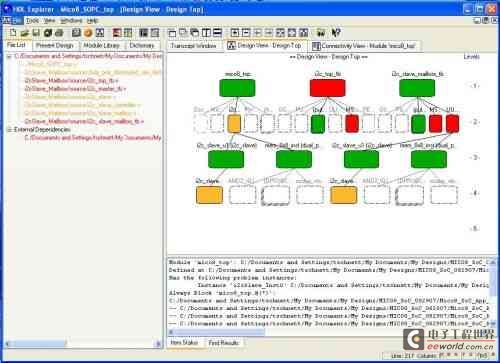

嵌入式微控制器IP可以描述整個設計,或者作為一個大型設計的一部分與附加代碼結合在一起。尋找一種有助于設計HDL調試和規則檢查的工具是非常明智的。這種工具會生成該設計的分層結構和互連性的圖形表示。用戶可以通過各種圖形和分層結構來觀察設計,并利用智能工具交互探測視圖以發現各種問題。

圖6:設計視圖—HDL調試工具

這對于IP集成的維護和復雜FPGAHDL設計的重設計都是很有用的,IP集成需要全面深入的途徑進行設計分析和管理。相比傳統仿真器或綜合工具,這種工具可以實現設計結構的更高層抽象。這有助于創建并管理文檔以及分析設計結構,從而極大地減少了花費在這些項目上的設計時間。

功能仿真

功能仿真首先創建一個工作庫,設計被編譯到該工作庫中。仿真器通過圖形用戶接口、菜單或命令行使該過程更加順利。這其中包含了設計文檔和測試向量(test bench)。測試向量實例化該設計,并將數據加載到輸入端。當運行設計時,測試向量被應用于該設計并顯示結果(通常以波形的形式)進行分析。

可利用各種仿真器實現設計的功能仿真。如果已對整個系統建模,則可以在系統級進行功能仿真,或者對單個設計單元進行仿真以確保正確的語法和功能已在RTL級建模。在這種特殊情況下,有兩家OEM的仿真器可供選擇。Aldec公司的Active-HDL Lattice Designer Edition Lite是一種附加的仿真環境。它不但提供混合語言VHDL和Verilog仿真,還可提供面向FPGA設計的可選設計流程。另一種選擇是MentorGraphics的ModelSim,它能夠提供VHDL和Verilog語言以及門級時序仿真,以對設計

進行完整的仿真和分析。

綜合

一旦完成功能仿真,下一步就是綜合。綜合可以用獨立的方式完成,或者在供應商的項目導航工具中作為后臺函數運行。綜合獲取設計、進行邏輯優化并實現工藝映射。獨立模式綜合的步驟包括建立項目、加入源文件、設置約束、運行設計和分析結果。約束是綜合的實現選項,例如扇出限制、使用全局置位/復位。屬性則附屬于對象,以控制其依附的特定對象的優化、映射和分析。目前可提供兩種領先的綜合工具。

Precision RTL綜合工具是Mentor Graphics公司的重要RTL綜合解決方案。利用Precision RTL界面可以很容易地獲取有用的特性和工具,例如示意圖(RTL/工藝)觀察器、約束分析器、PreciseTime(用于高級時序分析)、支持時序調整(re-timing)等等。這些高級工具有助于改進效率并最終優化結果。

Synplicity公司的Synplify綜合工具是一款高性能、復雜的邏輯綜合引擎,它利用專有的行為提取綜合技術(Behavior Extracting Synthesis Technology)提供快速、高效的FPGA和CPLD設計。簡單的用戶接口和強大的綜合引擎結合在一起能迅速提供優化的結果。

評論