用一只引腳為微控制器輸入并行數據

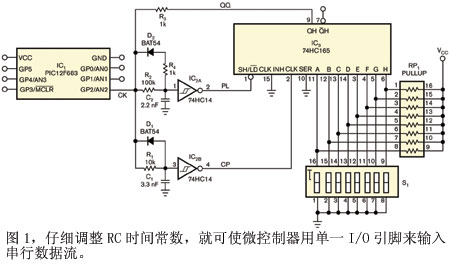

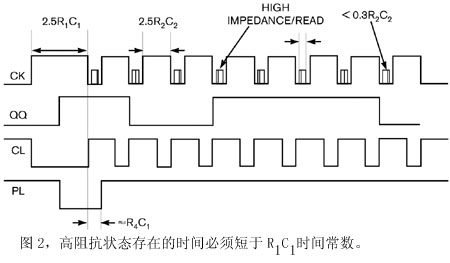

PL信號上升后,微控制器的I/O端口上的較短脈沖在移位寄存器的時鐘輸入端CP(不是在PL輸入端)產生脈沖。這些時鐘脈沖的持續時間必須足夠長,應超過延時R1C1,但不能超過R2C2。這些時鐘脈沖使數據移位,使得8比特在移位寄存器輸出端QQ順序出現。

如果微控制器的數據方向短暫地改變,以便借助高阻抗輸入,那么上述移位寄存器數據會占支配地位,這是由于R1、R2、R3的相對值所致,R3值低得多。高阻抗狀態存在的時間必須短于R1C1時間常數(圖2)。微控制器現在讀取單一數據比特。三個不同周期的作用產生了三種功能:加載、時鐘、數據讀取。微控制器改變端口方向、讀取引腳數據、把引腳方向重設為輸出所需的時間決定了時序。例如,1ms微控制器需要10ms。

為避免假CP脈沖,該時間常數必須低于0.33R1C1,因此R1C1可以是30ms,而R2C2可以是200ms。這些設置允許在大約1ms內完成一次8比特讀取。為實現更快操作,可把RC繼電器換成精密可再觸發單穩多頻振蕩器(如NXP公司的74HC123)和邏輯門。可用更多移位寄存器擴充此方案,來讀取數十個信號。

請注意:74HC165移位寄存器中的內部邏輯阻止CP信號在LD處于有效狀態時使數據移位。電阻器R4確保LD和CP的正確順序。二極管D1和D2使每個電容迅速放電,來“復位”R1C1和R2C2的延時功能。

評論