基于8086 CPU的單芯片計算機系統(tǒng)的設計

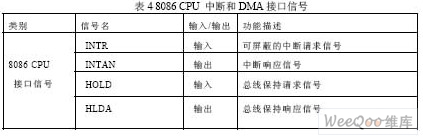

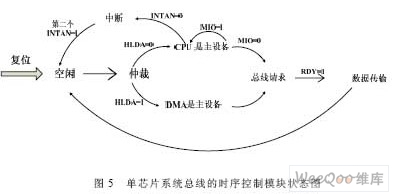

系統(tǒng)總線在接收到外設的中斷請求之后,會向CPU 提出中斷申請,一旦接收到中斷響應,要向外設傳送中斷響應信號,同時修改譯碼單元,選通該外設,保證在第二個中斷響應期間能將中斷類型號通過總線傳送給CPU,使得CPU 能成功跳轉到中斷服務子程序。

DMA 控制器在執(zhí)行數(shù)據(jù)傳輸時,需要掌握AHB 總線的控制權,向片上存儲器或者總線上其他外設發(fā)出地址和控制信號,即相當于AMBA 的主設備;另一方面,在DMA 控制器啟動工作之前,CPU 需要對其進行預處理操作,以使其按照特定的配置參數(shù)進行工作,在這個初始化階段,CPU 是AHB 總線上的主設備,DMA 控制器屬于從設備。基于DMA控制器的這種兩面性,在總線設計中配備了專門的DMA 通道與其相匹配:CPU 正常工作時,

DMA 扮演從設備的角色,接受CPU 對其的初始化;利用HLDA 作仲裁信號,當CPU 響應外設DMA 請求時(即HLDA 為高電平),讓出總線控制權給外設,利用DMA 數(shù)據(jù)通道傳輸數(shù)據(jù),傳輸?shù)膮f(xié)議同樣遵從AMBA 協(xié)議。總線的時序控制模塊狀態(tài)如圖5 所示。

3.3 存儲單元的接口設計

存儲器子系統(tǒng)包括一個RAM 和一個ROM,8086CPU 支持20 位地址總線,具有1M 字節(jié)存儲空間,分為RAM 區(qū)和ROM 區(qū)。本文利用開發(fā)板的片上ROM 資源配置成16k*16 的格式作為存儲器中的ROM 單元,采用DE2 開發(fā)板上的8M 的SDRAM 配置成256K*16 位總線格式代替存儲器中的RAM 單元。

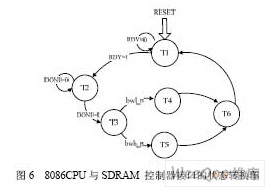

在各種隨機存儲器件中,SDRAM 的價格低,體積小,速度快,容量大,是比較理想的器件。但SDRAM 的控制邏輯比較復雜,對時序要求也十分嚴格,這就要求有一個專門的控制器:控制SDRAM 的初始化,刷新和預沖以及基本的讀寫操作。同時,需要匹配SDRAM控制器和8086 CPU 的讀寫時序。該接口具體實現(xiàn)的狀態(tài)機如圖6 所示。

T1:當RDY 為高電平時,首先確定是進行讀還是寫操作,這時DONE 為0:讀:設置WR=0,RD=1; 寫:設置WR=1,RD=0。

T2:當DONE 信號為高電平,表示可以進行讀/寫操作,跳轉到T3。

T3:CPU 通過SDRAM 控制器對SDRAM 進行讀寫操作。

T4:當?shù)妥止?jié)有效信號bwl_n 為高電平時,執(zhí)行低字節(jié)傳輸。

T5:當高字節(jié)有效信號bwh_n 為高電平時,執(zhí)行高字節(jié)傳輸。

T6:CPU 完成讀寫操作,相關控制信號清零。

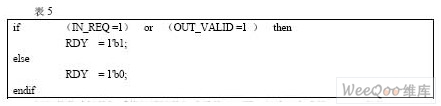

其中,DONE 信號用于指示是否讀寫完成,只有DONE 為高電平時表示讀寫完成,才能進行下次讀寫操作。RDY 信號表示SDRAM 是否做好準備接受CPU 的訪問,由SDRAM的寫請求信號(IN_REQ =1)和讀有效信號(OUT_VALID =1 )共同控制,其產(chǎn)生過程偽碼如表5 所示。

根據(jù)單芯片計算機系統(tǒng)級設計的組成結構,調用已經(jīng)編寫完成的8086 IP 軟核、8255 IP軟核、SDRAM 控制器、SDRAM 模型IS42S16400、AHB 總線 IP 軟核以及譯碼器IP 軟核。

連接相應的輸入輸出端口,同時對8086 相關的輸入端口進行賦值,將未使用的輸出端口懸空,完成單芯片計算機系統(tǒng)的RTL 級設計。

4 單芯片計算機系統(tǒng)的仿真與驗證

單芯片計算機的RTL 級設計只是全部設計流程的一部分,為保證最終設計的成功,必須對其進行全面的軟件仿真與硬件驗證,包括搭建測試平臺,設計測試方案以及分析仿真結果,實現(xiàn)FPGA 驗證。

4.1 測試方案的設計

在包含8255 應用電路的單芯片計算機系統(tǒng)搭建完成的基礎上,要求實現(xiàn)八個開關量控制八個LED燈亮滅的功能。將八個開關量連接8255 的PA0~PA7;將八個LED 燈驅動電路連接8255 的PC0~PC7。在8086 CPU 的控制下,通過總線讀取連接在8255 PA 口的八個開關量,將開關值送往SDRAM 存儲,再從SDRAM 讀取開關量發(fā)送到8255 PC 口,使其驅動八個LED 燈的亮或滅。

4.2 仿真結果分析

單芯片計算機最小集的RTL 級仿真波形,如圖7 所示。在8086 CPU 的控制下,8255接口讀取連接在8255 PA 口的八個開關量11000010 以后,將其發(fā)送到8255 的PC 口,驅動輸出邏輯值11000010。

使用QuartusII 軟件成功編譯設計,將布局布線生成的結果下載到FPGA 中,得到與設計等效的實際電路,對實際的電路用測試系統(tǒng)進行測試,從而驗證設計的正確性。將FPGA的驗證結果經(jīng)邏輯分析儀讀取顯示,如圖8 所示。

5 結束語

本論文在基于集成電路設計方法學的指導下,探討了一種基于8086 CPU 核的單芯片計算機平臺的架構,研究了其與AMBA 總線、SDRAM、8255 等外圍IP 的集成。在此基礎上,設計基于8086 IP 軟核的單芯片計算機系統(tǒng),并實現(xiàn)了FPGA 功能演示。在后續(xù)的工作中,將考慮進一步擴展CPU 外圍接口IP 軟核;集成DMA 控制器,實現(xiàn)VGA 顯示功能;將DOS 操作系統(tǒng)加入8086 單芯片計算機平臺,并開發(fā)在操作系統(tǒng)下的設備驅動程序和應用軟件。

評論