S3C2440的LCD編程

1. LCD工作的硬件需求:

要使一塊LCD正常的顯示文字或圖像,不僅需要LCD驅動器,而且還需要相應的LCD控制器。在通常情況下,生產廠商把LCD驅動器會以 COF/COG的 形式與LCD玻璃基板制作在一起,而LCD控制器則是由外部的電路來實現,現在很多的MCU內部都集成了LCD控制器,如S3C2410/2440等。通 過LCD控制器就可以產生LCD驅動器所需要的控制信號來控制STN/TFT屏了。

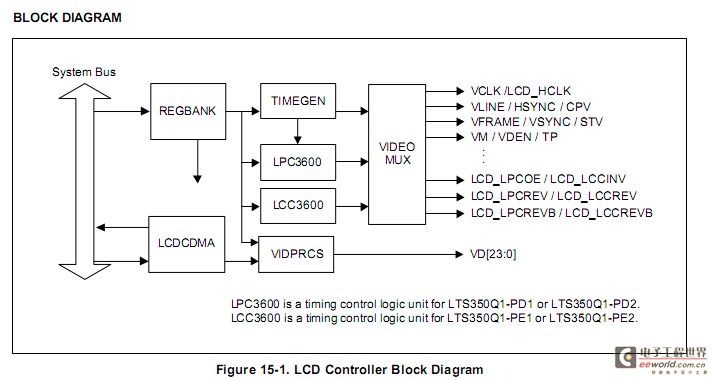

2. S3C2440內部LCD控制器結構圖:

我們根據數據手冊來描述一下這個集成在S3C2440內部的LCD控制器:

a:LCD控制器由REGBANK、LCDCDMA、TIMEGEN、VIDPRCS寄存器組成;

b:REGBANK由17個可編程的寄存器組和一塊256*16的調色板內存組成,它們用來配置LCD控制器的;

c:LCDCDMA是一個專用的DMA,它能自動地把在偵內存中的視頻數據傳送到LCD驅動器,通過使用這個DMA通道,視頻數據在不需要CPU的干預的情況下顯示在LCD屏上;

d:VIDPRCS接收來自LCDCDMA的數據,將數據轉換為合適的數據格式,比如說4/8位單掃,4位雙掃顯示模式,然后通過數據端口VD[23:0]傳送視頻數據到LCD驅動器;

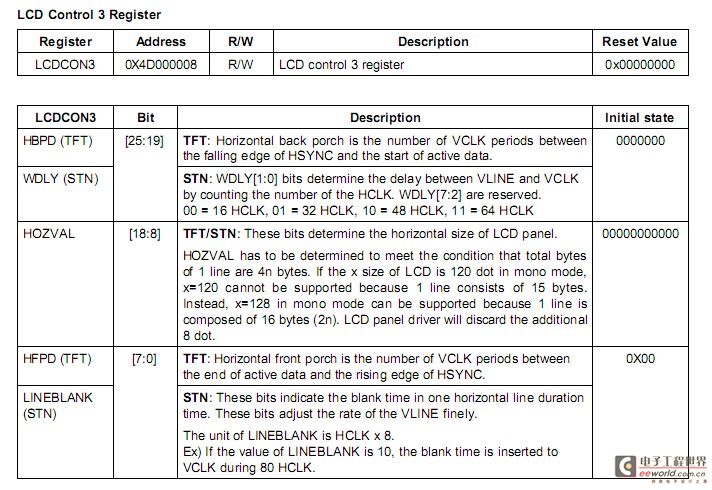

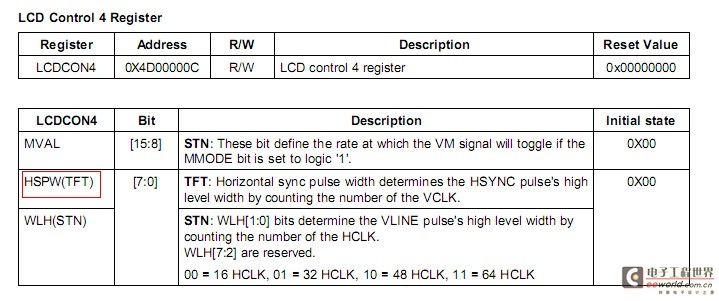

e:TIMEGEN由 可編程的邏輯組成,他生成LCD驅動器需要的控制信號,比如VSYNC、HSYNC、VCLK和LEND等,而這些控制信號又與REGBANK寄存器組中 的LCDCON1/2/3/4/5的配置密切相關,通過不同的配置,TIMEGEN就能產生這些信號的不同形態,從而支持不同的LCD驅動器(即不同的 STN/TFT屏)。

FIFO存儲器位于LCDCDMA.。當FIFO空或部分空時,LCDCDMA要求從幀緩沖中取來要顯示的圖像數據,而這個幀緩沖是LCD控制 器在RAM中開辟的一片緩沖區。當這個傳輸請求被存儲控制器中的總線仲裁器接收到后,從系統存儲器到內部FIFO就會成功傳輸4個字節。FIFO的總大小 是28個字,其中低位FIFOL是12個字,高位FIFOH是16個字。

3. 常見TFT屏工作時序分析:

LCD提供的外部接口信號:

VSYNC/VFRAME/STV:垂直同步信號(TFT)/幀同步信號(STN)/SEC TFT信號;

HSYNC/VLINE/CPV:水平同步信號(TFT)/行同步脈沖信號(STN)/SEC TFT信號;

VCLK/LCD_HCLK:象素時鐘信號(TFT/STN)/SEC TFT信號;

VD[23:0]:LCD像素數據輸出端口(TFT/STN/SEC TFT);

VDEN/VM/TP:數據使能信號(TFT)/LCD驅動交流偏置信號(STN)/SEC TFT 信號;

LEND/STH:行結束信號(TFT)/SEC TFT信號;

LCD_LPCOE:SEC TFT OE信號;

LCD_LPCREV:SEC TFT REV信號;

LCD_LPCREVB:SEC TFT REVB信號。

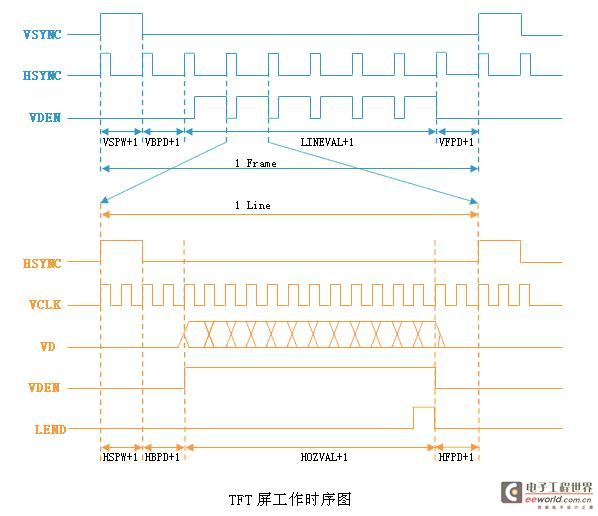

所有顯示器顯示圖像的原理都是從上到下,從左到右的。這是什么意思呢?這么說吧,一副圖像可以看做是一個矩形,由很多排列整齊的點一行一行組成,這些點稱之為像素。那么這幅圖在LCD上的顯示原理就是:

A:顯示指針從矩形左上角的第一行第一個點開始,一個點一個點的在LCD上顯示,在上面的時序圖上用時間線表示就為VCLK,我們稱之為像素時鐘信號;

B:當顯示指針一直顯示到矩形的右邊就結束這一行,那么這一行的動作在上面的時序圖中就稱之為1 Line;

C:接下來顯示指針又回到矩形的左邊從第二行開始顯示,注意,顯示指針在從第一行的右邊回到第二行的左邊是需要一定的時間的,我們稱之為行切換;

D:如此類推,顯示指針就這樣一行一行的顯示至矩形的右下角才把一副圖顯示完成。因此,這一行一行的顯示在時間線上看,就是時序圖上的HSYNC;

E: 然 而,LCD的顯示并不是對一副圖像快速的顯示一下,為了持續和穩定的在LCD上顯示,就需要切換到另一幅圖上(另一幅圖可以和上一副圖一樣或者不一樣,目 的只是為了將圖像持續的顯示在LCD上)。那么這一副一副的圖像就稱之為幀,在時序圖上就表示為1 Frame,因此從時序圖上可以看出1 Line只是1 Frame中的一行;

F:同樣的,在幀與幀切換之間也是需要一定的時間的,我們稱之為幀切換,那么LCD整個顯示的過程在時間線上看,就可表示為時序圖上的VSYNC。

上面時序圖上各時鐘延時參數的含義如下:(這些參數的值,LCD產生廠商會提供相應的數據手冊)

VBPD(vertical back porch):表示在一幀圖像開始時,垂直同步信號以后的無效的行數,對應驅動中的upper_margin;

VFBD(vertical front porch):表示在一幀圖像結束后,垂直同步信號以前的無效的行數,對應驅動中的lower_margin;

VSPW(vertical sync pulse width):表示垂直同步脈沖的寬度,用行數計算,對應驅動中的vsync_len;

HBPD(horizontal back porch):表示從水平同步信號開始到一行的有效數據開始之間的VCLK的個數,對應驅動中的left_margin;

HFPD(horizontal front porth):表示一行的有效數據結束到下一個水平同步信號開始之間的VCLK的個數,對應驅動中的right_margin;

HSPW(horizontal sync pulse width):表示水平同步信號的寬度,用VCLK計算,對應驅動中的hsync_len;

注:對于一個已知尺寸的LCD屏,只要確定了VCLK值,行頻和場頻就應該知道了。但這樣還不行的,因為在每一幀時鐘信號中,還會有一些與屏顯示無關的時鐘出現,這就給確定行頻和場頻帶來了一定的復雜性。如在HSYNC信號先后會有水平同步信號前肩(HFPD)和水平同步信號后肩(HBPD)出現,在VSYNC信號先后會有垂直同步信號前肩(VFPD)和垂直同步信號后肩(VBPD)出現,在這些信號時序內,不會有有效像素信號出現,另外HSYNC和VSYNC信號有效時,其電平要保持一定的時間,它們分別叫做水平同步信號脈寬HSPW和垂直同步信號脈寬VSPW,這段時間也不能有像素信號。因此計算行頻和場頻時,一定要包括這些信號。

評論