那么下面我們開始講解一下相應(yīng)的程序語言吧。我用的單片機(jī)芯片是加強(qiáng)型的51單片機(jī)C8051F020,它都外擴(kuò)了一些功能,如AD、DA、溫度傳感器,但是核心還是沒有改變的。要與FPGA進(jìn)行通信,我用Quartus II的VHDL語言進(jìn)行編程。也就是說,單片機(jī)與FPGA都要進(jìn)行相應(yīng)的端口設(shè)置。

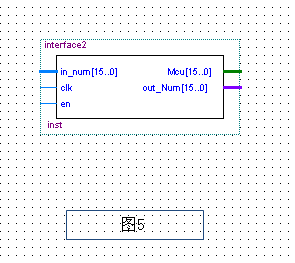

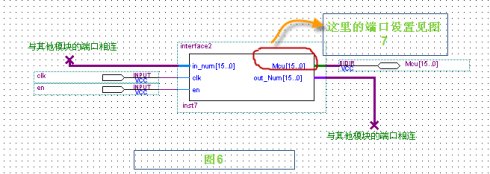

先講解一下FPGA方面的編程,如圖5,這是在Quartus II界面里的圖形

其中端口含義如下:in_num[15..0]——代表要從FPGA向單片機(jī)傳輸?shù)臄?shù)據(jù)總線

out_num[15..0]——代表要從單片機(jī)傳送給FPGA的數(shù)據(jù)總線,它與in_num[15..0]在直

接與其它的端口(軟件界面里面)直接與其它端口連接

Mcu[15..0]——代表硬件上要與單片機(jī)連接的端口。

clk---則是時(shí)鐘信號(hào),

en--使能信號(hào),當(dāng)它為高的時(shí)候,則單片機(jī)向FPGA傳輸數(shù)據(jù),否則傳輸方向相反。

對(duì)應(yīng)的VHDL放言如下:

library ieee;

use ieee.std_logic_1164.all;

entity interface2 is

port(Mcu:inout std_logic_vector(15 downto 0);

in_num:in std_logic_vector(15 downto 0);

out_Num:out std_logic_vector(15 downto 0);

clk:in std_logic;

en:in std_logic);

end interface2;

architecture rtl of interface2 is

signal a,b:std_logic_vector(15 downto 0);

begin

common: process(clk)

begin

if(clkevent and clk=1)then

a<=in_num;

out_num<=b;

end if;

end process;

Wri_Read:process(en,Mcu)

begin

if(en=1)then

Mcu<=(others=>Z);--

b<=Mcu;

else

Mcu<=a;--當(dāng)en=0的時(shí)候,就作為輸出端口

end if;

end process;

end rtl;

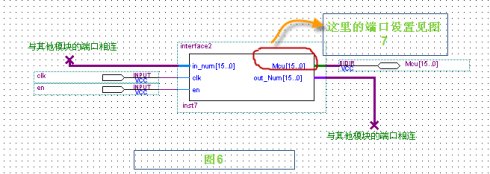

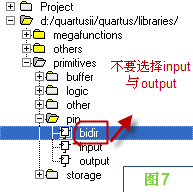

這里有幾個(gè)注意點(diǎn):一、首先最好只用一個(gè)雙向口,也就是我這里的Mcu[15..0],另外一個(gè)“雙向口”則等效成一個(gè)輸入口與一個(gè)輸出口,也就是這里in_num[15..0]與out_num[15..0].否則會(huì)有麻煩的。 因?yàn)槿绻贿@么做,那么在Quartus里面與這個(gè)雙向口相連的端口必須都要設(shè)成雙向口,這樣的話,嘿嘿...

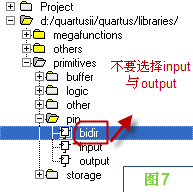

二、與那個(gè)Mcu[15..0]相聯(lián)系的端口必須是雙向口的,具體圖解如下。

最后,進(jìn)行單片機(jī)方面的設(shè)置了,其中最重要的就是端口初始化了。如下:

//這個(gè)是FPGA要求的,當(dāng)從FPGA里讀取數(shù)據(jù)時(shí)所要滿足的條件

//眾所周知,在雙向口的設(shè)置中,對(duì)于端口的輸入與輸出的設(shè)置是最重要的

//輸入時(shí)一定要記得把雙向口的輸出設(shè)置為高阻狀態(tài),在單片機(jī)中要記得設(shè)置為漏極開路

//當(dāng)輸出要記得把單片機(jī)設(shè)置為推挽輸出,否則設(shè)置為漏極開路的話是達(dá)不到效果 的

voidReadData(void)

{

en=0;//這部分要與fpga聯(lián)合起來設(shè)置P1MDOUT=0x00;//此時(shí)單片機(jī)設(shè)置為漏極開路,在對(duì)端口寫1時(shí)才能呈現(xiàn)高阻狀態(tài)

P74OUT=0x00;//這里我用的單片機(jī)是用P1口與P4口用來傳輸數(shù)據(jù)的

P1=0xff;//對(duì)應(yīng)端口寫1,設(shè)置成高阻狀態(tài)

P4=0xff;//對(duì)應(yīng)端口寫1,設(shè)置成高阻狀態(tài)

}

//這個(gè)也是FPGA要求的,當(dāng)往FPGA里寫入數(shù)據(jù)時(shí)所要滿足的條件

voidWriteData(void)

{

en=1;//當(dāng)en=1時(shí),我要向fpga里面寫數(shù)據(jù)了,

P1MDOUT=0xff;//寫數(shù)據(jù)的時(shí)候,別忘記把對(duì)應(yīng)的端口改成用推挽方式

P74OUT=0x03;//不用的引腳設(shè)成漏極開路的狀態(tài).當(dāng)輸出的方式時(shí)才把它設(shè)為推挽輸出

}

好了,到現(xiàn)在為止,我已經(jīng)把我知道都寫在這里了。如果認(rèn)為我這篇文章對(duì)你有幫助的話,還請(qǐng)多多支持。回貼是一種美德。

評(píng)論