3.11 線路空閑多處理器模式(待續(xù))

3.12 地址位多處理器模式(待續(xù))

3.13 自動波特率檢測(待續(xù))

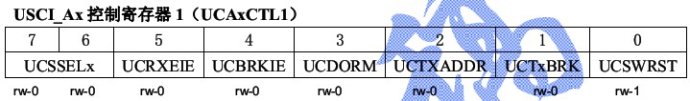

3.2

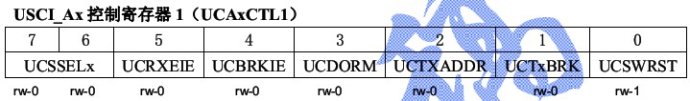

此寄存器主要是配置USCI,PUC后時鐘選擇外部時鐘,所以初始化時除了置位 UCSWRST 位外還需配置時鐘源。其它的默認(rèn)就行。

四、低功耗 UART模式下使用 USCI模塊

USCI 模塊提供低功耗模式下的自動時鐘激活功能。當(dāng) USCI 時鐘源由于設(shè)備處于低功耗模式不活動時,無論時鐘源的控制位如何設(shè)置,USCI 模塊會在需要時激活時鐘源,時鐘將保持活動狀態(tài)直到 USCI模塊返回空閑狀態(tài)。USCI模塊返回到閑狀態(tài)后,將反轉(zhuǎn)時鐘源控制位的設(shè)置。

eg.

void InitUARTA1(void)

{

UCA1CTL1 |= UCSWRST;// PUC后,UCSWRST位自動置位,這使 USCI保持在復(fù)位狀態(tài)

UCA1CTL0 = 0x00;

UCA1CTL1 |= UCSSEL_2; // SMCLK

UCA1BR0 = 216; // 24MHz 115200

UCA1BR1 = 0; // 24MHz 115200

UCA1MCTL = UCBRS_2 + UCBRF_0; //0x04+0x00

P5SEL = 0xC0; // P5.6/7 = USCI_A0 TXD/RXD

UCA1CTL1 &= ~UCSWRST; // **Initialize USCI state machine**,。清除UCSWRST 將釋放 USCI, UCA1IE |= UCRXIE; // Enable USCI_A1 RX interrupt

}

#pragma vector = USCI_A1_VECTOR

__interrupt void USCI_A1_ISR(void)

{

switch (__even_in_range(UCA1IV,4))

{

case 0:break;

case 2:

g_uartBufA[g_bufALen] = UCA1RXBUF;

if (g_uartBufA[g_bufALen]==0xFF)

{

}

if (g_uartBufA[g_bufALen++]==0xFD) //判斷PC機(jī)發(fā)送的命令幀是否已完

{

g_bufALen=0;

g_uartReceive = 1;// 置位

}

break;

case 4:break; // Vector 4 - TXIFG

default: break;

}

}

void USciSend( )

{

unsigned char i;

for (i = 0; i <g_bufALen; i++)

{

while (!(UCA1IFG & UCTXIFG));

UCA1TXBUF = g_uartBufA[uartBuf1];

}

}//UCA1MCTL 是UCA1的調(diào)制控制寄存器

五、波特率的產(chǎn)生

USCI 波特率發(fā)生器可以從非標(biāo)準(zhǔn)源頻率中產(chǎn)生標(biāo)準(zhǔn)的波特率,可以通過UCOS16位選擇系統(tǒng)提供的兩種操作模式。波特率可以通過使用BRCLK 產(chǎn)生,根據(jù) UCSSELx設(shè)置,BRCLK 可以作為外部時鐘 UCAxCLK或內(nèi)部時鐘ACLK 或SMCLK 的時鐘源。

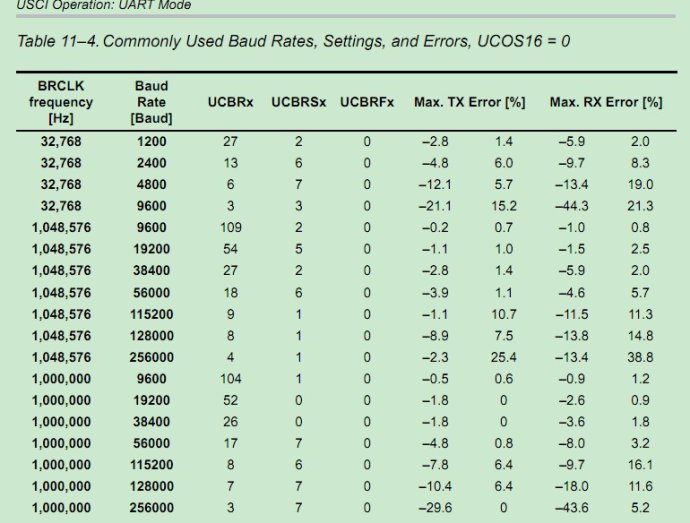

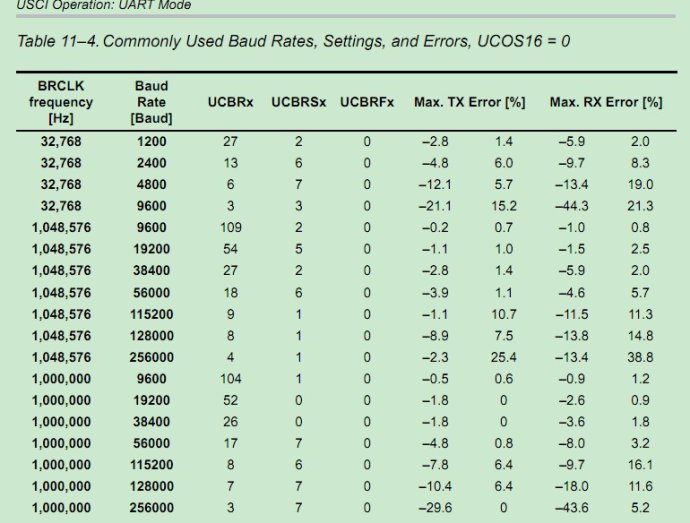

5.1低頻波特率

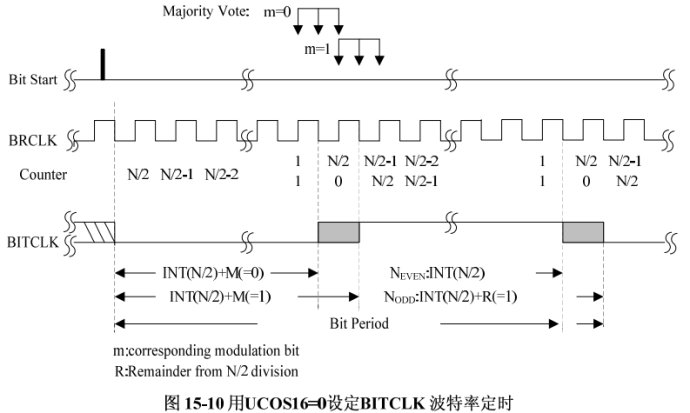

當(dāng)UCOS16=0 時選擇低頻模式。該模式允許從低頻時鐘源產(chǎn)生波特率(例如從32768Hz 晶振產(chǎn)生9600波特)。通過使用較低的輸入頻率,可以降低模塊的功耗。在高頻和高分頻設(shè)置下使用這種模式,將會使多數(shù)表決在逐漸縮小的窗口中執(zhí)行,因此會降低多數(shù)表決法的優(yōu)勢(下面的例子都是這種模式)。

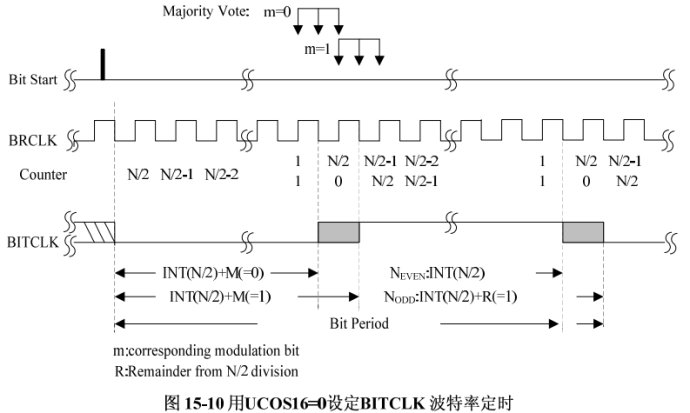

在低頻模式下,波特率發(fā)生器使用1個預(yù)分頻器和1個調(diào)制器產(chǎn)生位時鐘時序。這種組合下,產(chǎn)生波特率時支持小數(shù)分頻;在這種模式下,最大的 USCI波特率是UART 源時鐘頻率 BRCLK的1/3 。

每一位的時序如圖所示,對于接收的每一位,為了確定該位的值,采用多數(shù)表決法。這些采樣點(diǎn)發(fā)生在N/2-1/2,N/2 和N/2 + 1/2 個BRCLK 周期處,這里N 是每個BITCLK 時鐘中 BRCLKs 的數(shù)值。

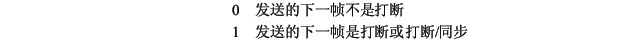

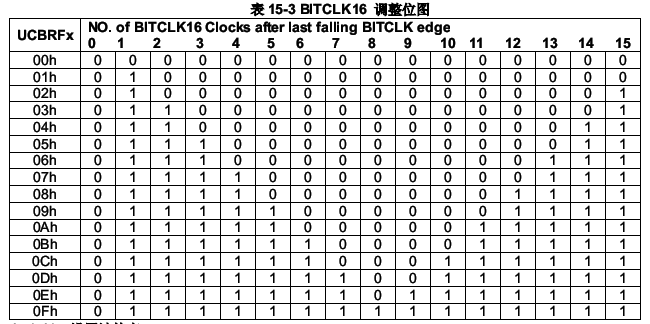

調(diào)制是建立在如表15-2 所示的 UCBRSx 設(shè)置基礎(chǔ)上的。表中1個1 表示m= 1,相應(yīng)的BITCLK 周期是一個BRCLK 周期,它比m=0 時的BITCLK 周期長。調(diào)制在8位后進(jìn)行,但以新的開始位重新啟動。

5.2 過采樣波特率的產(chǎn)生

當(dāng)UCOS16=1時,選擇過采樣模式。該模式支持在較高輸入時鐘頻率下對UART 位流采樣。在多數(shù)表決方法的結(jié)果總是一個位時鐘周期的1/16位置。當(dāng)使能IrDA 編碼器和解碼器時,這種模式也支持帶有3/16位時間的IrDA脈沖。

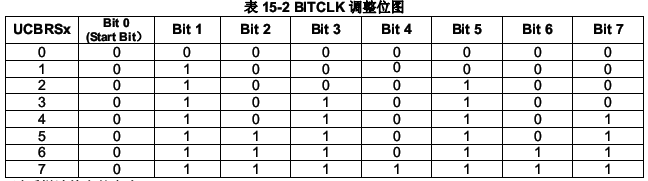

該模式使用一個預(yù)分頻器和調(diào)制器產(chǎn)生BITCLK16 時鐘,該時鐘比 BITCLK 快16倍。這種組合方式支持波特率產(chǎn)生時 BITCLK16 和BITCLK 的小數(shù)分頻。在這種情況下,最大的USCI 波特率是 UART源時鐘頻率BRCLK的1/16。當(dāng)UCBRx 設(shè)置為0或1時,將忽略第一級分頻器和調(diào)制器,BRCLK等于 BITCLK16—在這種情況下BITCLK16沒有調(diào)制,因此將忽略 UCBRFx位。

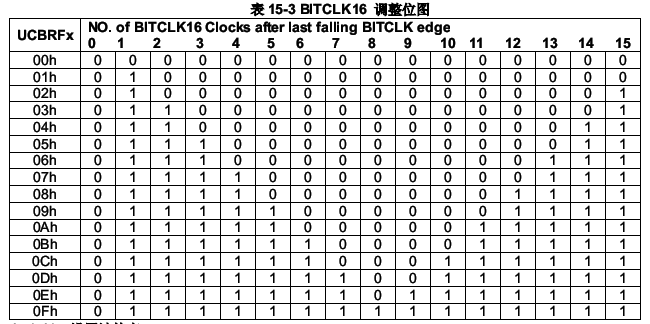

BITCLK16 調(diào)制是建立在如表15-3 所示的 UCBRFx 設(shè)置基礎(chǔ)上的。表中1個1 表示相應(yīng)的 BITCLK16 周期一個BRCLK周期,它比m=0 時的BITCLK16周期長。以每一個新位時序開始調(diào)制;BITCLK調(diào)制是建立在如前所述的 UCBRSx設(shè)置(見表15-2)基礎(chǔ)上的。

5.3 設(shè)置波特率

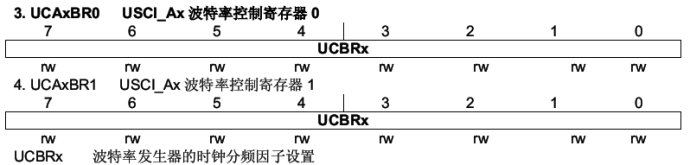

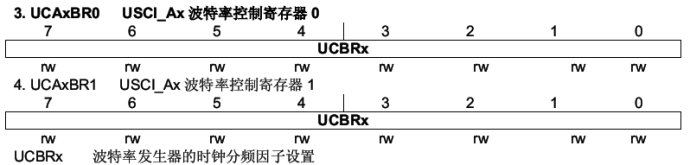

430的波特率設(shè)置用三個寄存器實(shí)現(xiàn):

UxBR0:波特率發(fā)生器分頻系數(shù)低8位;

UxBR1:波特率發(fā)生器分頻系數(shù)高8位;

UxMCTL:波特率發(fā)生器分頻系數(shù)的小數(shù)部分實(shí)現(xiàn);

對于給定的BRCLK時鐘源,所使用的波特率將決定分頻因子 N:N = fBRCLK/波特率。分頻因子N 通常不是一個整數(shù)值,因此至少需要一個分頻器和一個調(diào)制器來盡可能接近分頻因子,如果N 值等于或大于16,可以通過置位UCOS16 選擇過采樣波特率產(chǎn)生模式。

在低頻模式下,分頻因子的整數(shù)部分通過預(yù)分頻器實(shí)現(xiàn)UCBRx = INT(N);

小數(shù)部分由帶有下面nominal公式的調(diào)制器實(shí)現(xiàn):UCBRSx = round((N–INT(N))× 8),(round表示舍入)

UCBRSx計數(shù)值增1或減1,對任何給定的位給一個較小的最大比特誤差。為了檢測是不是這種情況,對于每個UCBRSx設(shè)置的每一位都必須經(jīng)過詳細(xì)的誤差計算;

在過采樣模式下,預(yù)分頻器設(shè)置為:UCBRx = INT(N/16),第一階調(diào)制器設(shè)置為:UCBRFx = round(((N/16)– INT(N/16) ) × 16 ),當(dāng)需要更高精度時,UCBRSx調(diào)制器可以實(shí)現(xiàn)從 0到7 的值。對于給定位,為了找到最低的最大誤碼率設(shè)置,對于帶有初始UCBRFx設(shè)置和增1 或減 1的 UCBRFx設(shè)置的 UCBRSx從0到7的所有設(shè)置,都必須經(jīng)過詳細(xì)的誤差計算。

下面詳解上例中的四條語句:

UCA1CTL1 |= UCSSEL_2; // SMCLK

UCA1BR0 = 216; // 24MHz 115200

UCA1BR1 = 0; // 24MHz 115200

UCA1MCTL = UCBRS_2 + UCBRF_0; //0x04+0x00

這里 SMCLK 已在時鐘部分初始化,其時鐘源為: Fdcoclkdiv = (760+1)*32768 = 24.936448 MHZ;

分頻系數(shù) N = 24936448/115200 = 216.462222,UCA1BR0是分頻系統(tǒng)整數(shù)部分的低8位、UCA1BR1是高8位,所以..

UCA1MCTL 是波特率發(fā)生器分頻系數(shù)的小數(shù)部分,由于是低頻模式(UCOS16=0),UCA1MCTL 寄存器中的UCBRFx 位忽略,而UCBRSx = round((N–INT(N))× 8) 即 UCBRSx = 0.46×8 四舍五入取為 4。

UCBRSx 的值也可以這么解釋: 0.46*8=3.68 四舍五入為 4個1,把這4個1分成8位均勻排開 01010101 (LSB在前),對照表15-2 查得UCBRSx=0x04。

評論