ARM·微處理器的編程模型

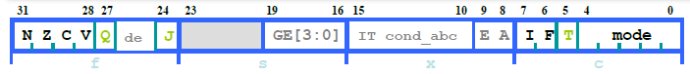

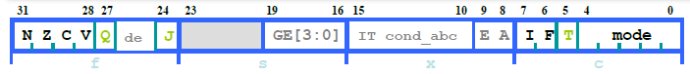

2)程序狀態寄存器(CPSR)

·mode:表示處理器的工作狀態

·T:0,ARM state;1,Thumb state ;

·interrupt disable bits

I=1:Disables the IRQ

F=1:Disable the FIO

·condition code flags

N = Negative result from ALU (非零)

Z = Zero result from ALU (結果是零)

C = ALU operation Carried out (進位)

V = ALU operation Overflowed

v5,v6的

Q:dsp擴展單元

J:java加速器

(處理器用于存儲數據方式有兩種,分為大字節序和小字節序

大字節序:高字節在低位,低字節在高位

小字節序:高字節在高位,低字節在低位

*老版本只支持小字字節,現在都支持,linux網絡編程采用大字節序)

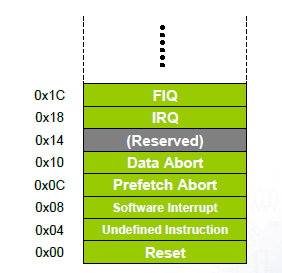

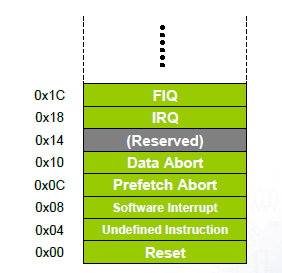

【ARM所支持的異常】

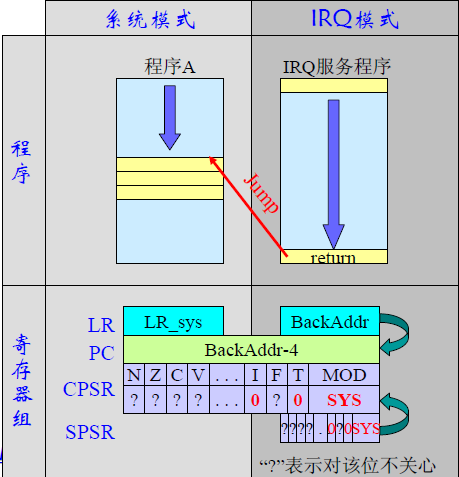

(只要正常的程序流被暫時中止,處理器將進入異常模式。在處理異常之前,ARM9內核保存的當前的處理器狀態(CPSR->SPSR),這樣當處理器結束時可以恢復執行原來的程序(SPSR->CPSR))

Reset:復位中斷 ;

Reset:復位中斷 ;

Undefineed Instruction :未定義指令;

Software Interrupt:軟件中斷

Prefetch Abort:預取指令中止 ;

Date Abort :數據中止 ;

IRQ:外部中斷 ;

FIQ:快速中斷請求 ;

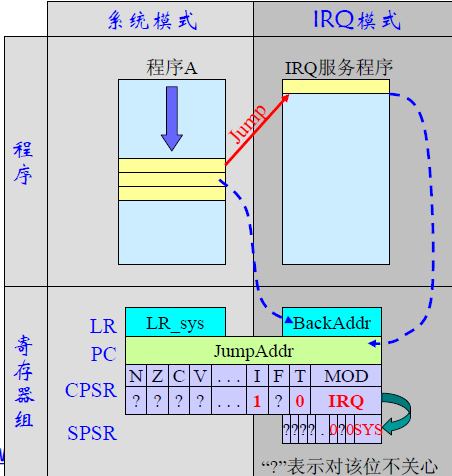

【異常的響應】

1)進入異常:

*LR中保存當前執行指令的下一條指令的地址:LR=PC-4

*CPSR->SPSR (保留狀態)

*CPSR->與異常類型相對應的狀態

*PC從相關異常向量處取址

*跳轉,執行命令

評論