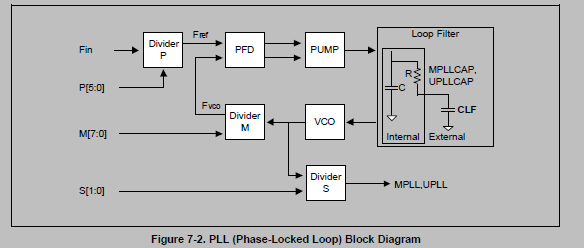

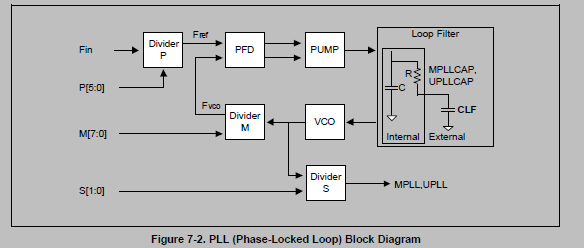

S3C2440的默認工作主頻有兩種12MHz和16.9344MHz,也就是我們的晶振的頻率,但一般12MHz的晶振用的比較多,Fin就是指我們接的晶振頻率。大家都知道s3c2440上電正常工作后頻率是遠遠大于12MHz和16.9344MHz的,我們的s3c2440的cpu正常工作時的頻率就是405MHz,因此這就需要一個電路來提升頻率,在s3c2440的datasheet中找到了這個電路,下面這個就是PLL電路:

本文引用地址:http://www.104case.com/article/201611/320978.htm 由圖中可以看出,Fin進去后,經過PLL電路,最終輸出兩個PLL信號頻率即MPLL和UPLL,這兩個又是什么呢

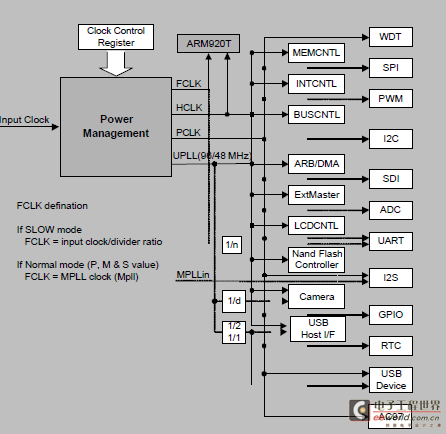

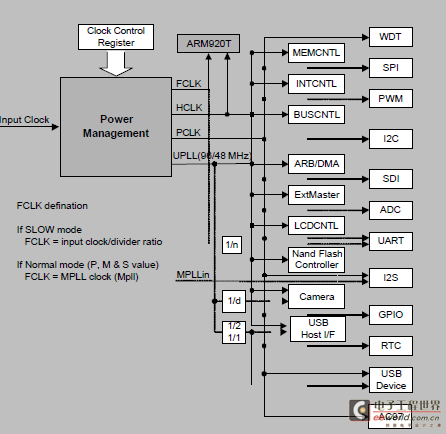

UPLL是專用于USB設備的,MPLL是用于CPU及外圍電路的,不清楚,還是得找s3c2440的datasheet,下面這就是從datasheet中截取的:

圖中給出了各種接口設備使用的時鐘信號

UPLL是USB專用,這里就不講了,下面重點講下MPLL,剛才已經說了MPLL主要用于CPU和外圍設備,但外圍設備和CPU的工作頻率并不一樣啊,CPU的工作頻率肯定比外設要高,這就必然要對MPLL進行處理,于是FCLK,HCLK,PCLK就登場了

首先講下FCLK,首先看下datasheet中的介紹:

The Clock control logic in S3C2440A can generate the required clock signals including FCLK for CPU, HCLK for the

AHB bus peripherals, and PCLK for the APB bus peripherals.

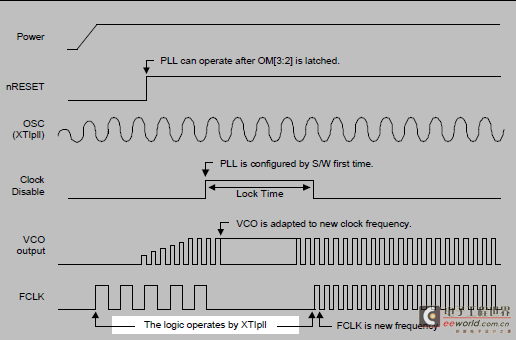

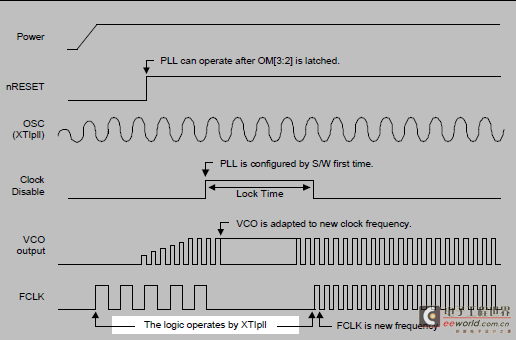

相信搞嵌入式的都能看的懂,FCLK是CPU用的,HCLK是AHB總線用的,比如說SDRAM,PCLK是APB總線用的,比如說UART。這三個我們一個個來講解,首先看FCLK,CPU用的,看datasheet中的關于FCLK的時序圖,我們就會看出一些東東。

從上面的圖中可以看到FCLK在CPU上電后,過了一段時間就發生了比較大的變化,明顯值變大了,從上面這個圖中我們可以大致看出s3c2440上電啟動過程:

1、上電幾毫秒后(power由低變高),晶振輸出穩定,此時FCLK=晶振頻率,nRESET信號恢復高電平后,CPU開始執行指令。

2、我們可以在程序開頭啟動MPLL,在設置MPLL的幾個寄存器后,需要等待一段時間(Lock Time),MPLL的輸出才穩定。在這段時間(Lock Time)內,FCLK停振,CPU停止工作。Lock Time的長短由寄存器LOCKTIME設定。

評論