ARM在線升級FPGA程序方法(逆向工程)

公司有款產品采用FPGA做處理器,需要

要實現該功能有幾種方式:

1. 解析編譯出的FPGA下載文件jic、pof,將解析后的內容燒錄到EPCS4中。但是否這兩種文件格式公開存儲結構呢?芯片廠商是否對此保密?

2. 直接讀取EPCS4的程序,燒錄到另一塊EPCS4中。但是否讀取的EPCS4內容以及根據FPGA序列號做了加密呢?

權衡任務安排時間,選擇第二種方案,畢竟就算第一種方案可行,也需要設計第二方案的讀寫操作。 可喜的是這次逆向工程就這么搞定了。

具體實現

ARM用IO模擬SPI總線燒FPGA配置芯片EPCS4完成軟件升級,在TQ2440上測試,工程可以通過下面的 github連接獲得。該工程與TQ2440平臺定制,在其他平臺未必能運行,建議只看 BitOpt.h,EPCS4.c,EPCSxx.h,mainboot.c

升級步驟:

1、

2、

讀取的數據是最終執行的二進制Bin文件,因為Altera開發環境所生成的jic、pof與最終EPCS4內的內容不一樣(除非找到生成Bin的方法)。之所以讀取“所有扇區”數據是因為不知道實際Bin文件大小,干脆全部讀出。EPCS4存儲空間是512KB。IO模擬SPI時序的方式速度有限,讀/寫512KB各需要40S,用SPI總線速度會快不少。該方法已經在2塊FPGA里運行沒問題,證明Bin文件并沒有在燒寫過程中綁定FPGA芯片序列號。

演示:

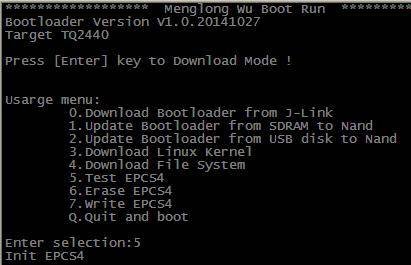

啟動后按“5”進入EPCS4測試代碼。

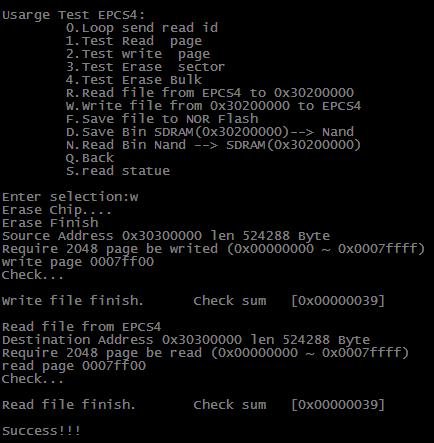

按“N”將Bin文件從Nand拷貝到SDRAM的0x30200000,長度512KB。

按“W”將0x30200000的數據燒錄到EPCS4中,寫入后計算寫入前數據校驗碼得0x00000039,然后再讀出EPCS4中“所有”數據,計算讀出內容的校驗碼也是0x00000039,比較校驗移植返回“Success!!!”,否則返回“Check sum Error!!!”。

硬件連接:

升級過程中FPGA需要掉電,或者將FPGA與EPCSxx連接的引腳斷開,否則3個設備連接到共用信號線無法通信。

EPCS4驅動編寫、移植注意事項:

1、

2、

3、

4、

5、

6、

7、

正確的命令是:CS拉低——發送命令1——CS拉高;CS拉低——發送命令2——CS拉高;

不允許:CS拉低——發送命令1——發送命令2——CS拉高;

建議移植代碼測試步驟

1、讀取芯片ID號(silicon ID或Device Identification)

2、如果讀取錯誤的話用示波表查看時序,保證CLK脈沖周期大于40ns,以及MOSI發送的內容正確(Read silicon ID——0xAB或Read silicon ID——0x 9F)。

3、讀取扇區內容。

4、擦除、寫入(寫入前必須先擦除)所有扇區,并讀出寫入數據。

5、讀取EPCSxx數據在NandFlash里建立bin文件,最后燒寫到EPCSxx能運行

6、與節點管理器添加更新FPGA通信協議

評論