S3C2440時鐘電源管理

含有兩個鎖相環MPLL、UPLL產生系統所需要的不同頻率的時鐘

MPLL:

為CPU產生FCLK時鐘

為AHB產生HCLK時鐘

為APB產生PCLK時鐘

UPLL:

為usb(Host and Device)產生UCLK(48M)

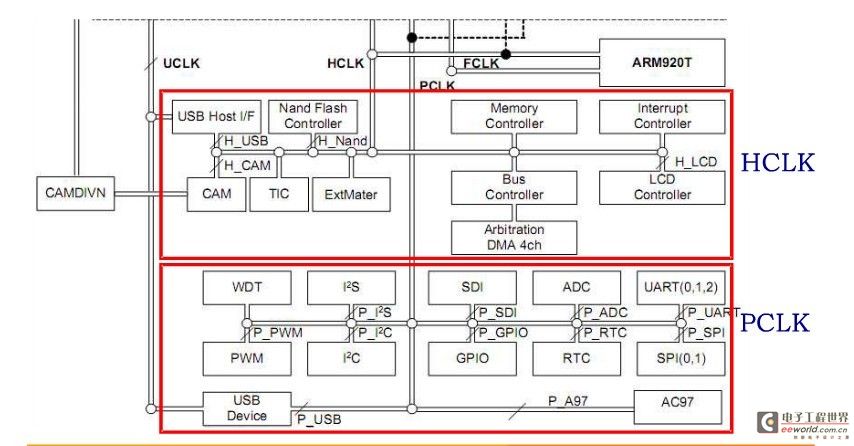

FCLK,HCLK和 PCLK

FCLK是提供給ARM920T 的時鐘。

HCLK 是提供給用于 ARM920T,存儲器控制器,中斷控制器,LCD 控制器,DMA 和 USB 主機模塊的 AHB

總線的時鐘。

PCLK 是提供給用于外設如WDT,IIS,I2C,PWM 定時器,MMC/SD 接口,ADC,UART,GPIO,RTC 和

SPI的APB 總線的時鐘。

下圖為PLL(鎖相環)方框圖

設置FCLK要用到PLL控制寄存器MPLLCON

例如:如果外部晶振Fin為12MHZ,設置FCLK為400MHZ,

由公式Fout = 2 × m × Fin / ( p*2^s) 此處:m =MDIV+8, p=PDIV+2, s=SDIV

可知rMPLLCON=((92<<12)|(1<<4)|1) 其中(MDIV=92, PDIV=1,SDIV=1)。

下面的這個函數是配置FCLK HCLK PCLK的比例的函數,用到時鐘分頻寄存器CLKDIVN

- voidChangeClockDivider(inthdivn,intpdivn)

- {

- //hdivn,pdivnFCLK:HCLK:PCLK

- //0,01:1:1

- //0,11:1:2

- //1,01:2:2

- //1,11:2:4

- //2,01:4:4

- //2,11:4:8

- //3,01:3:3

- //3,11:3:6

- rCLKDIVN=(hdivn<<1)|pdivn;

- if(hdivn==2)

- rCAMDIVN=(rCAMDIVN&~(3<<8))|(1<<9);

- if(hdivn==3)

- rCAMDIVN=(rCAMDIVN&~(3<<8))|(1<<8);

- }

[cpp]view plaincopy

- //**************************[UPLL]*******************************

- voidChangeUPllValue(intmdiv,intpdiv,intsdiv)//配置UPLLCON寄存器

- {

- rUPLLCON=(mdiv<<12)|(pdiv<<4)|sdiv;

- }

[cpp]view plaincopy

- voidCalcBusClk(void)//計算總線頻率

- {

- U32val;

- U8m,p,s;

- val=rMPLLCON;

- m=(val>>12)&0xff;

- p=(val>>4)&0x3f;

- s=val&3;

- //(m+8)*FIN*2不要超出32位數!

- FCLK=((m+8)*(FIN/100)*2)/((p+2)*(1<

- val=rCLKDIVN;

- m=(val>>1)&3;//HDIVN的值

- p=val&1;//PDIVN的值

- val=rCAMDIVN;

- s=val>>8;//CAMDIVN[8:9],為HDIVN分頻改變位

- switch(m)//計算HCLK頻率

- {

- case0:

- HCLK=FCLK;

- break;

- case1:

- HCLK=FCLK>>1;

- break;

- case2:

- if(s&2)//見CAMDIVN寄存器HCLK4_HALF

- HCLK=FCLK>>3;

- else

- HCLK=FCLK>>2;

- break;

- case3:

- if(s&1)//見CAMDIVN寄存器HCLK3_HALF

- HCLK=FCLK/6;

- else

- HCLK=FCLK/3;

- break;

- }

- if(p)//計算PCLK頻率

- PCLK=HCLK>>1;

- else

- PCLK=HCLK;

- val=rUPLLCON;

- m=(val>>12)&0xff;

- p=(val>>4)&0x3f;

- s=val&3;

- UPLL=((m+8)*FIN)/((p+2)*(1<

- UCLK=(rCLKDIVN&8)?(UPLL>>1):UPLL;//計算UCLK頻率

- }

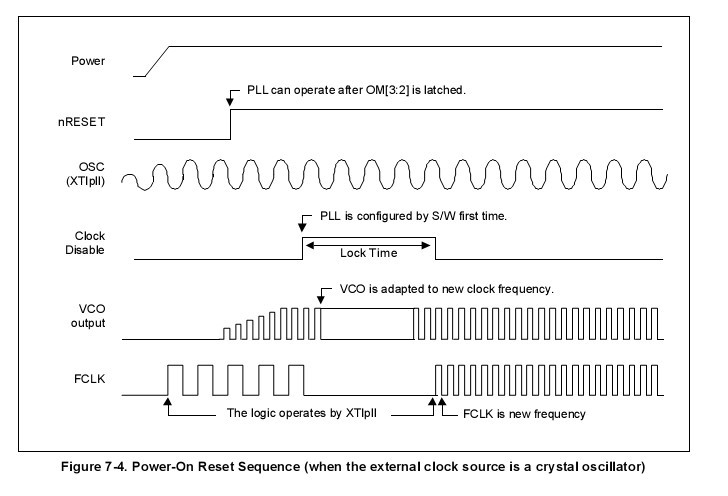

下圖為外部時鐘為晶振時的上電復位順序

評論