基于ARM的嵌入式Linux移植真實體驗(1)――基本概念

ARM是Advanced RISC Machines(高級精簡指令系統處理器)的縮寫,是ARM公司提供的一種微處理器知識產權(IP)核。

ARM的應用已遍及工業控制、消費類電子產品、通信系統、網絡系統、無線系統等各類產品市場。基于ARM 技術的微處理器應用約占據了32位RISC 微處理器75%以上的市場份額。揭開你的手機、MP3、 PDA,嘿嘿,里面多半藏著一個基于ARM的微處理器!

ARM內核的數個系列(ARM7、ARM9、ARM9E、ARM10E、SecurCore、Xscale、StrongARM),各自滿足不同應用領域的需求,無孔不入的滲入嵌入式系統各個角落的應用。這是一個ARM的時代!

下面的圖片顯示了ARM的隨處可見:

有人的地方就有江湖(《武林外傳》),有嵌入式系統的地方就有ARM。

構建一個復雜的嵌入式系統,僅有硬件是不夠的,我們還需要進行操作系統的移植。我們通常在ARM平臺上構建Windows CE、Linux、Palm OS等操作系統,其中Linux具有開放源代碼的優點。

下圖顯示了基于ARM嵌入式系統中軟件與硬件的關系:

日前,筆者作為某嵌入式ARM(硬件)/Linux(軟件)系統的項目負責人,帶領項目組成員進行了下述工作:

(1)基于ARM920T內核S3C2410A CPU的電路板設計;

(2)ARM處理下底層軟件平臺搭建:

a.Bootloader的移植;

b.嵌入式Linux操作系統內核的移植;

c.嵌入式Linux操作系統根文件系統的創建;

d.電路板上外設Linux驅動程序的編寫。

本文將真實地再現本項目開發過程中作者的心得,以便與廣大讀者共勉。第一章將簡單地介紹本ARM開發板的硬件設計,第二章分析Bootloader的移植方法,第三章敘述嵌入式 Linux的移植及文件系統的構建方法,第四章講解外設的驅動程序設計,第五章給出一個已構建好的軟硬件平臺上應用開發的實例。

如果您有良好的嵌入式系統開發基礎,您將非常容易領會本文講解地內容。即便是您從來沒有嵌入式系統的開發經歷,本文也力求讓您讀起來不覺得生澀。您可以通過如下email與作者聯系:21cnbao@21cn.com。

2.ARM體系結構

作為一種RISC體系結構的微處理器,ARM微處理器具有RISC體系結構的典型特征。還具有如下增強特點:

(l)在每條數據處理指令當中,都控制算術邏輯單元(ALU)和移位器,以使ALU和移位器獲得最大的利用率;

(2)自動遞增和自動遞減的尋址模式,以優化程序中的循環;

(3)同時Load和Store多條指令,以增加數據吞吐量;

(4)所有指令都條件執行,以增大執行吞吐量。

ARM體系結構的字長為32位,它們都支持Byte(8位)、Halfword(16位)和Word(32位)3種數據類型。

ARM處理器支持7種處理器模式,如下表:

大部分應用程序都在User模式下運行。當處理器處于User模式下時,執行的程序無法訪問一些被保護的系統資源,也不能改變模式,否則就會導致一次異常。對系統資源的使用由操作系統來控制。

User模式之外的其它幾種模式也稱為特權模式,它們可以完全訪問系統資源,可以自由地改變模式。其中的FIQ、IRQ、supervisor、Abort和undefined 5種模式也被稱為異常模式。在處理特定的異常時,系統進入這幾種模式。這5種異常模式都有各自的額外的寄存器,用于避免在發生異常的時候與用戶模式下的程序發生沖突。

還有一種模式是system模式,任何異常都不會導致進入這一模式,而且它使用的寄存器和User模式下基本相同。它是一種特權模式,用于有訪問系統資源請求而又需要避免使用額外的寄存器的操作系統任務。

程序員可見的ARM寄存器共有37個:31個通用寄存器以及6個針對ARM處理器的不同工作模式所設立的專用狀態寄存器,如下圖:

ARM9采用5級流水線操作:指令預取、譯碼、執行、數據緩沖、寫回。ARM9設置了16個字的數據緩沖和4個字的地址緩沖。這5級流水已被很多的RISC處理器所采用,被看作RISC結構的“經典”。

3.硬件設計

3.1 S3C2410A微控制器

電路板上的ARM微控制器S3C2410A采用了ARM920T核,它由ARM9TDMI、存儲管理單元MMU和高速緩存三部分組成。其中,MMU可以管理虛擬內存,高速緩存由獨立的16KB地址和16KB數據高速Cache組成。ARM920T有兩個內部協處理器:CP14和CP15。CP14用于調試控制,CP15用于存儲系統控制以及測試控制。

S3C2410A集成了大量的內部電路和外圍接口:

Ø LCD控制器(支持STN和TFT帶有觸摸屏的液晶顯示屏)

Ø SDRAM控制器

Ø 3個通道的UART

Ø 4個通道的DMA

Ø 4個具有PWM功能的計時器和一個內部時鐘

Ø 8通道的10位ADC

Ø 觸摸屏接口

Ø I2C總線接口

Ø 12S總線接口

Ø 兩個USB主機接口

Ø 一個USB設備接口

Ø 兩個SPI接口

Ø SD接口

Ø MMC卡接口

S3C2410A集成了一個具有日歷功能的RTC和具有PLL(MPLL和UPLL)的芯片時鐘發生器。MPLL產生主時鐘,能夠使處理器工作頻率最高達到203MHz。這個工作頻率能夠使處理器輕松運行WinCE、Linux等操作系統以及進行較為復雜的信息處理。UPLL則產生實現USB模塊的時鐘。

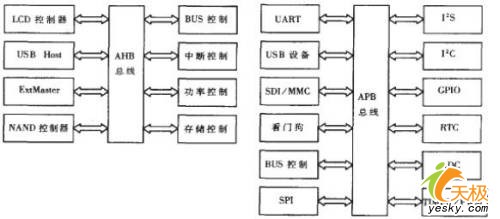

下圖顯示了S3C2410A的集成資源和外圍接口:

我們需要對上圖中的AHB總線和APB總線的概念進行一番解釋。ARM核開發的目的,是使其作為復雜片上系統的一個處理單元來應用的,所以還必須提供一個ARM與其它片上宏單元通信的接口。為了減少不必要的設計資源的浪費,ARM公司定義了AMBA(Advanced Microcontroller Bus Architecture)總線規范,它是一組針對基于ARM核的、片上系統之間通信而設計的、標準的、開放協議。

在AMBA總線規范中,定義了3種總線:

(l)AHB—Advanced High Performace Bus,用于高性能系統模塊的連接,支持突發模式數據傳輸和事務分割;

(2)ASB—Advanced System Bus,也用于高性能系統模塊的連接,支持突發模式數據傳輸,這是較老的系統總線格式,后來由AHB總線替代;

(3)APB—Advanced PeriPheral Bus,用于較低性能外設的簡單連接,一般是接在AHB或ASB系統總線上的第二級總線。

典型的AMBA總線系統如下圖:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/69udv233i8pd.jpg" />

S3C2410A將系統的存儲空間分成8個bank,每個bank的大小是128M字節,共1G字節。Bank0到bank5的開始地址是固定的,用于ROM或SRAM。bank6和bank7可用于ROM、SRAM或SDRAM。所有內存塊的訪問周期都可編程,外部Wait也能擴展訪問周期。下圖給出了S3C2410A的內存組織:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/g5l8t1g2z6tes.jpg" />

下圖給出了S3C2410A的數據總線、地址總線和片選電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/3849z191nff5s.jpg" />

SDRAM控制信號、集成USB接口電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/5qhw81in5n35s.jpg" />

內核與存儲單元供電電路(S3C2410A對于片內的各個部件采用了獨立的電源供給,內核采用1.8V供電,存儲單元采用3.3V獨立供電):

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/286a6i39817vs.jpg" />

JTAG標準通過邊界掃描技術提供了對電路板上每一元件的功能、互聯及相互間影響進行測試的方法,極大地方便了系統電路的調試。

測試接入端口TAP的管腳定義如下:

Ø TCK:專用的邏輯測試時鐘,時鐘上升沿按串行方式對測試指令、數據及控制信號進行移位操作,下降沿用于對輸出信號移位操作;

Ø TMS:測試模式選擇,在TCK上升沿有效的邏輯測試控制信號;

Ø TDI:測試數據輸入,用于接收測試數據與測試指令;

Ø TDO:測試數據輸出,用于測試數據的輸出。

S3C2410A調試用JTAG接口電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/4pq5i0220olm.jpg" />

3.2 SDRAM存儲器

SDRAM被用來存放操作系統(從FLASH解壓縮拷入)以及存放各類動態數據,采用SAMSUNG公司的K4S561632,它是4Mxl6bitx4bank的同步DRAM,容量為32MB。用2片K4S561632實現位擴展,使數據總線寬度達到32bit,總容量達到64MB,將其地址空間映射在S3C2410A的bank6。

SDRAM 所有的輸入和輸出都與系統時鐘CL K上升沿同步,由輸入信號RA S、CA S、WE組合產生SDRAM 控制命令,其基本的控制命令如下:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/8tnz2jm9zr77.jpg" />

SDRAM 在具體操作之前首先必須通過MRS命令設置模式寄存器,以便確定SDRAM 的列地址延遲、突發類型、突發長度等工作模式;再通過ACT命令激活對應地址的組,同時輸入行地址;然后通過RD 或WR 命令輸入列地址,將相應數據讀出或寫入對應的地址;操作完成后用PCH 命令或BT 命令中止讀或寫操作。在沒有操作的時候,每隔一段時間必須用ARF命令刷新數據,防止數據丟失。

下圖給出了SDRAM的連接電路:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/1i6eu87v4s10s.jpg" />

3.3 FLASH存儲器

NOR和NAND是現在市場上兩種主要的非易失閃存技術。

NOR的特點是芯片內執行(XIP,Execute In Place),即應用程序可直接在Flash閃存內運行,不必把代碼讀到系統RAM中。NOR的傳輸效率很高,在1~4MB的小容量時具有很高的成本效益,但是很低的寫入和擦除速度大大影響了它的性能。

NAND結構能提供極高的單元密度,可以達到高存儲密度,并且寫入和擦除的速度也很快。應用NAND的困難在于Flash的管理和需要特殊的系統接口,S3C2410A內嵌了NAND FLASH控制器。

S3C2410A支持從GCS0上的NOR FLASH啟動(16位或32位)或從NAND FLASH啟動,需要通過OM0和OM1上電時的上下拉來設置:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/ssk71un6t4l1.jpg" />

在系統中分別采用了一片NOR FLASH(28F640)和NAND FLASH(K9S1208),電路如下圖:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/7ix3rbe188p5s.jpg" />

3.4串口

S3C2410內部集成了UART控制器,實現了并串轉換。外部還需提供CMOS/TTL電平與RS232之間的轉換:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/skbuv4xq1f4o.jpg" />

3.5以太網

以太網控制芯片采用CIRRUS LOGIC公司生產的CS8900A,其突出特點是使用靈活,其物理層接口、數據傳輸模式和工作模式等都能根據需要而動態調整,通過內部寄存器的設置來適應不同的應用環境。它符合IEEE803.3以太網標準,帶有傳送、接收低通濾波的10Base-T連接端口,支持10Base2,10Base5和10Base-F的AUI接口,并能自動生成報頭,自動進行CRC檢驗,在沖突后自動重發。

CS8900A支持的傳輸模式有I/O和Memory模式。當CS8900A有硬件復位或軟件復位時,它將默認成為8位工作模式。因此,要使CS8900A工作于16位模式,系統必須在訪問之前提供給總線高位使能管腳(/SBHE)一個由高到低、再由低到高變化的電平。

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/2323iwdi4v89s.jpg" />

3.6 USB接口

USB 系統由USB 主機(USB Host)、USB集線器(USB Hub)和USB設備(USB Device)組成。USB 和主機系統的接口稱作主機控制器(Host Controller),它是由硬件和軟件結合實現的。根集線器是綜合于主機系統內部的,用以提供USB的連接點。USB的設備包括集線器(Hub)和功能器件(Function)。

S3C2410A集成了USB host和USB device,外部連接電路如下圖:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/t9143dw950y6.jpg" />

3.7電源

LDO(Low Dropout)屬于DC/DC變換器中的降壓變換器,它具有低成本、低噪聲、低功耗等突出優點,另外它所需要的外圍器件也很少,通常只有 1~2 個旁路電容。

在電路板上我們分別用兩個LDO來實現5V向3.3V(存儲接口電平)和1.8V(ARM內核電平)的轉換。

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/110hhvh95i1e.jpg" />

up監控電路采用MAX708芯片,提供上電、掉電以及降壓情況下的復位輸出及低電平有效的人工復位輸出:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/82ptl9b9g07r.jpg" />

3.8其它

SN74LVTH62245A提供總線驅動和緩沖能力:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/7i9pfpcx6et6s.jpg" />

S3C2410A集成LCD液晶顯示器控制電路,外部引出接口:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/8t32s961ih5u.jpg" />

觸摸屏有電阻式、電容式等,其本質是一種將手指在屏幕上的觸點位置轉化為電信號的傳感器。手指觸到屏幕,引起觸點位置電阻或電容的變化,再通過檢測這一電性變化,從而獲得手指的坐標位置。通過S3C2410A集成的AD功能,完成電信號向屏幕坐標的轉化,觸摸屏接口如下:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/e31e03427b9ms.jpg" />

鍵盤則直接利用CPU的可編程I/O口,若連接 mxn鍵盤,則需要m+n個可編程I/O口,由軟件實現鍵盤掃描,識別按鍵:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/lvoqhd8o5n8b.jpg" />

3.9整體架構

下圖呈現了ARM處理器及外圍電路的整體設計框架:

650) this.width=650;" onclick=window.open("http://blog.51cto.com/viewpic.php?refimg=" + this.src) alt="" src="http://dev.yesky.com/imagelist/06/32/t2658jh1iu8n.gif" />

4.小結

本章講解了基于S3C2410A ARM處理器電路板硬件設計的基本組成,為后續各章提供了總體性的準備工作。

評論