ARM處理器結構

ARM和Thumb狀態

RISC技術

流水線技術

超標量技術

ARM和Thumb狀態

V4版以后有:

(1)32位ARM指令集

(2)16位Thumb指令集,功能是ARM指令集的功能子集。

ARM7TDMI核以后,T變種的ARM微處理器有兩種工作狀態:

(1)ARM狀態

(2)Thumb狀態。

當ARM微處理器執行32位的ARM指令集時,工作在ARM狀態;

當ARM微處理器執行16位的Thumb指令集時,工作在Thumb狀態

Thumb技術介紹

ARM7體系結構被廣泛應用的時候,嵌入式控制器的市場仍然由8位、16位處理器占領。這些產品不能滿足高端應用。這些應用需要32位RISC處理器的性能和更優于16位CISC處理器的代碼密度。

為了解決代碼密度的問題,ARM增加了T變種。

Thumb從32位ARM指令集中抽出來的36條指令格式,可重新編成16位的操作碼。

在運行時,16位的Thumb指令又由處理器解壓成32位指令。

Thumb核有2套獨立的指令集,它使設計者得到ARM32位指令性能的同時,又能享有Thumb指令集產生的代碼方面的優勢,在性能和代碼大小之間取得平衡。

和ARM指令集相比,Thumb指令集具有以下的局限:

完成相同的操作,Thumb指令通常需要更多的指令,因此在對系統運行時間要求苛刻的場合,ARM指令集更為合適。

Thumb指令集沒有包含進行異常處理時需要的一些指令,因此在異常中斷時,還是需要使用ARM指令,這種限制決定了Thumb指令需要與ARM指令配合使用。

ARM與Thumb狀態轉換

在程序的執行過程中,微處理器可以隨時在兩種工作狀態之間切換,并且該轉變不影響處理器的工作模式和相應寄存器中的內容。

進入Thumb狀態:當操作數寄存器的狀態位(位[0])為1時,執行BX指令。

進入ARM狀態:當操作數寄存器的狀態位(位[0])為0時,執行BX指令。

RISC技術

嵌入式微處理器可以分為兩類:CISC和RISC;

CISC(Complex Instruction Set Computer):復雜指令系統計算機;隨著計算機技術的發展而不斷引入新的復雜的指令集,計算機的體系結構會越來越復雜。

大約有20%的指令會被反復使用,占整個程序代碼的80%,而余下的80%的指令卻不經常使用,在程序設計中只占20% 。

RISC(Reduced Instruction Set Computer):精簡指令系統計算機;- 采用固定長度的指令格式

- 使用單周期指令

- 大量使用寄存器

- 可用加載/存儲指令批量傳輸數據

- 在循環處理中使用地址的自動增減

RISC技術與CISC技術比較

RISC技術

ARM處理器采用加載/存儲(Load/Store)體系結構是典型的RISC處理器,即只有Load/Store的存/取指令可以訪問存儲器,其余指令都不允許進行存儲器操作。

RISC體系結構基本特點:

(1)大多數指令只需要執行簡單和基本的功能,其執行過程在一個機器周期內完成。

(2)只保留加載/存儲指令。操作數由加載/存儲指令從存儲器取出放寄存器內操作。

(3)芯片邏輯不采用或少采用微碼技術,而采用硬布線邏輯。

(4)減少指令數和尋址方式。

(5)指令格式固定,指令譯碼簡化。

(6)優化編譯。

RISC技術

ARM體系結構還采用了一些特別的技術:

所有的指令都可根據前面的執行結果決定是否被執行,提高了指令的執行效率。

可用Load/Store指令批量傳輸數據,以提高數據的傳輸效率。

可在一條數據處理指令中同時完成邏輯處理和移位處理。

RISC和CISC各有優勢,界限并不那么明顯。

現代的CPU往往采用CISC的外圍,內部加入了RISC的特性,如超常指令集CPU就是融合了RISC和CISC的優勢,成為未來的CPU發展方向之一。

流水線技術

是一種將每條指令分解為多步,并讓各步操作重疊,從而實現幾條指令并行處理的技術;

程序中的指令仍是一條條順序執行,但可以預先取若干條指令,并在當前指令尚未執行完時,提前啟動后續指令的另一些操作步驟,從而可加快程序的運行速度;

開發和設計嵌入式系統的過程中,CPU的性能是一個非常重要的考慮因素。

流水線技術是在本質上影響程序執行速度的因素。

由于計算機中一條指令的各個執行階段相對獨立,因此,現代CPU大多設計成流水線型的機器,在這種類型機器中幾個指令可以并行執行。采用流水線的重疊技術大大提高了CPU的運行效率。

當流水線內部的信息通暢流動時,CPU流水線能夠工作得最好。

但實際應用中,指令各執行階段的操作時間長短不同,有一些指令序列可能會打斷流水線內的信息流,所以有時流水線操作不十分通暢,會暫時降低CPU的執行速度。

單周期指令的執行過程

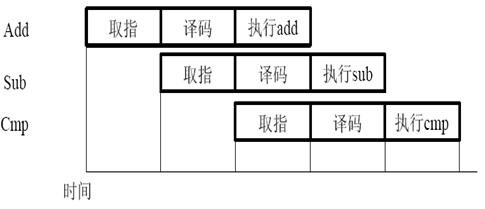

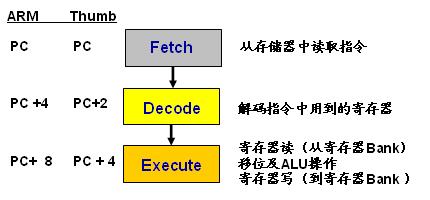

ARM的3級流水線

ARM7架構采用了一個3段的流水線:

(1)取指:將指令從內存中取出來。

(2)譯碼:操作碼和操作數被譯碼以決定執行什么功能。為下一周期準備數據路徑需要的控制信號。這一級指令”占有“譯碼邏輯,而不是”占有”數據路徑

(3)執行:執行已譯碼的指令。指令占有數據路徑,寄存器堆棧被讀取,操作數在桶行移位器中被移位。ALU產生運算結果并回寫到目的寄存器中,ALU結果根據指令需求更改狀態寄存器的條件位。

流水線模式下PC的更改過程

多周期ARM指令的3級流水線操作

數據路徑涉及到所有執行周期、地址計算和數據傳送。譯碼邏輯總是產生數據路徑在下一個周期使用的控制信號,因此除譯碼周期以外,在STR地址計算周期也產生數據傳送所需的控制信號。

取指的存儲器訪問和執行的數據路徑占用都是不可同時共享的資源,對于多周期指令來說,如果指令復雜以至于不能在單個時鐘周期內完成執行階段,就會產生流水線阻塞。

ARM的流水線設計問題

1)縮短程序執行時間:

Tprog:執行一個程序所需時間;

Ninst:執行該程序的指令條數;

CPI:執行每條指令的平均時鐘周期數;

Fclk:處理器的時鐘頻率。

措施:

提高時鐘頻率fclk(導致流水線的級數增加 )。

減少每條指令的平均時鐘周期數CPI(需要解決流水線的相關問題 )

2)解決流水線相關:

結構相關:某些指令在流水線中重疊執行時,產生資源沖突 。

措施:1)采用分離式指令Cache和數據Cache。2)ALU中采用單獨加法器來完成地址計算。

數據相關:當一條指令需要前面指令的執行結果,而這些指令均在流水線中重疊執行時,就可能引起流水線的數據相關。

數據相關有“寫后讀”、“寫后寫”和“讀后寫”等。

措施:1)旁路技術。2)流水線互鎖技術。

控制相關:當流水線遇到分支指令和其他會改變PC值的指令時,就會發生控制相關。

措施:1)引入延時分支。2)盡早計算出分支轉移成功時的PC值(即分支的目標地址)。

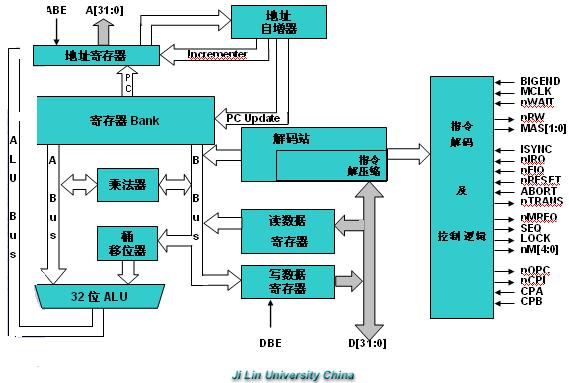

ARM的5級流水線

ARM9和StrongARM架構都采用了5級流水線.

增加了I-Cache和D-Cache,把存儲器的取指與數據存取分開;

增加了數據寫回的專門通路和寄存器;

把指令的執行過程分割為5部分:

取指:將指令從指令存儲器中取出,放入指令流水線中。

指令譯碼:對指令進行譯碼,從寄存器堆中讀取寄存器操作數。

執行:把一個操作數移位,產生ALU結果。如果指令是Load或Store,在ALU中計算存儲器的地址。

數據緩存:如果需要,訪問數據存儲器;否則,ALU的結果只是簡單地緩沖一個時鐘周期,以便使所有指令具有同樣地流水線流程。

寫回 :將指令產生地結果寫回到寄存器堆。

流水線對比

超標量執行

通過重復設置多套指令執行部件,同時處理并完成多條指令,實現并行操作,來達到提高處理速度的目的。

所有ARM內核,包括流行的ARM7、ARM9和ARM11等,都是單周期指令機。

ARM公司下一代處理器將是每周期能處理多重指令的超標量機。

超標量處理機:一個時鐘周期內同時執行多條指令的處理機。

超標量處理器中的多指令單元

超標量與流水線技術是兼容的,為了能夠在一個時鐘周期內同時發射多條指令,超標量處理機必須有兩條或兩條以上能夠同時工作的指令流水線。但與此同時,也帶來了多流水線的調度問題和操作部件的資源沖突問題。

超標量處理器在執行的過程中必須動態地檢查指令相關性。

如果代碼中有分支指令,必須將分支被執行和分支不被執行這兩種情況分開考慮。

計算執行時間幾乎是不可能的。

評論