ARM異常向量表初始化

CODE32

AREA Startup,CODE,READONLY

; /* 異常向量表 */

Vectors

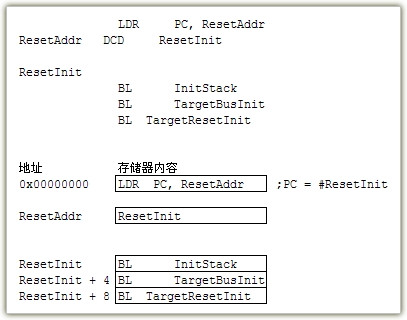

LDR PC,ResetAddr;把ResetAdde地址上的存儲器的內容裝載到PC上

LDR PC, UndefinedAddr

LDR PC, SWI_Addr

LDR PC, PrefetchAddr

LDR PC, DataAbortAddr

DCD 0

LDR PC, IRQ_Addr

LDR PC, FIQ_Addr

ResetAddr DCD ResetInit;為ResetAddr分配以ResetInit地址值,

UndefinedAddr DCD Undefined

SWI_Addr DCD SoftwareInterrupt

PrefetchAddr DCD PrefetchAbort

DataAbortAddr DCD DataAbort

Nouse DCD 0

IRQ_Addr DCD IRQ_Exception

FIQ_Addr DCD FIQ_Handler

此時ResetAddr實質上只作為一個指針(指向ResetInit),沒有分配空間,

ResetAddr地址的存儲器上裝載的是ResetInit的地址。

ResetInit

BL InitStack ; 初始化堆棧

BL TargetBusInit ; 總線系統初始化 (函數中不允許堆棧操作)

BLTargetResetInit; 針對目標板的系統初始化

以ResetInit為例,存儲器空間分配如下所示:

注意中斷向量表要存放在代碼段startup的開始處(Entry開始),而程序被鏈接時,該startup代碼段被鏈接在整個程序的入口地址。

=========================

1. undef exception handler

當前指令,如果CPU不支持,它會自動將該指令交給Co-processor.(如:MMU, FPU)處理。

如果Co-processor也無法識別這條指令,則產生異常.

當執行SWI指令時,產生這種中斷.

3. Data abort

由數據異常觸發.

通常有3種指令引發數據異常, 這些指令都是訪存操作.(都是由MMU引入后才可能會發生的情況)

LDR / STR

SWAP

LDM / STM

MMU的失效類型,又分為5種:

存儲訪問失效

地址對齊失效

地址變換失效

域控制器失效

訪問控制權限失效

因此當異常發生后,需要通過訪問CP15來獲知異常產生的具體原因和情況。

4. Pretetch Abort

對于ARM處理器來說,由于其內部使用了哈佛結構---獨立的數據的指令總線.

因此,在數據/指令的讀取過程中產生的異常也就很自然地可以區分開來

本質上而言,這些異常都是同屬于存儲訪問失敗產生的異常,因此這些異常都由MMU相關,在ARM手冊中DataAbort和PrefetchAbort都

稱為Memory abort。

Prefetch也就是在預取指令的動作后產生的,當處理器運行到這個無效的指令時(這個無效與undefined exception中的不可識別不同,

是指不存在或是無法得到)就觸發該異常。

評論