系統時鐘和定時器簡單記錄

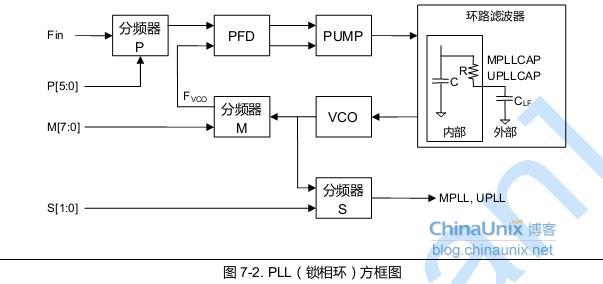

鎖相環(PLL):時鐘發生器之中作為一個電路的MPLL,參考輸入信號的頻率和相位同步出一個輸出信號。用于生成與輸入直流電壓成比例的輸出頻率的壓控振蕩器(VCO)、用于將輸入頻率(Fin)按p分頻的分頻器 P 、用于將VCO輸出頻率按m分頻并輸入到相位頻率檢測器(PFD)中的分頻器M用于將VCO輸出頻率按s分頻成為Mpll(輸出頻率來自MPLL模塊)的分頻器S、鑒相器、電荷泵以及環路濾波器。

鑒相器(PFD ):PFD檢測 Fref 和Fvco之間的相位差,并在檢測到相位差時產生一個控制信號(跟蹤信號)。Fref 意思為參考頻率。

電荷泵(PUMP )

電荷泵將PFD 控制信號轉換為一個按比例變化的電壓并通過外部濾波器來驅動 VCO。

電荷泵將PFD 控制信號轉換為一個按比例變化的電壓并通過外部濾波器來驅動 VCO。

環路濾波器

PFD產生用于電荷泵的控制信號,在每次 Fvco與Fref 比較時可能產生很大的偏差(紋波)。為了避免 VCO過載,使用低通濾波器采樣并且濾除控制信號的高頻分量。濾波器是一個典型由一個電阻和一個電容組成的單極性RC濾波器。

壓控振蕩器(VCO)

從環路濾波器的輸出電壓驅動 VCO,引起其振蕩頻率線性增大或減小,如同均勻變化電壓的功能。當Fvco與Fref 頻率和相位都在限期內相匹配時,PFD 停止發送控制信號給電荷泵,并轉變為穩定輸入電壓給環路濾波器。VCO頻率保持恒定,PLL 則保持固定為系統時鐘。

PFD產生用于電荷泵的控制信號,在每次 Fvco與Fref 比較時可能產生很大的偏差(紋波)。為了避免 VCO過載,使用低通濾波器采樣并且濾除控制信號的高頻分量。濾波器是一個典型由一個電阻和一個電容組成的單極性RC濾波器。

壓控振蕩器(VCO)

從環路濾波器的輸出電壓驅動 VCO,引起其振蕩頻率線性增大或減小,如同均勻變化電壓的功能。當Fvco與Fref 頻率和相位都在限期內相匹配時,PFD 停止發送控制信號給電荷泵,并轉變為穩定輸入電壓給環路濾波器。VCO頻率保持恒定,PLL 則保持固定為系統時鐘。

PLL和時鐘產生器的通常條件 (參見文檔)

如何控制鎖相環PLL的輸出頻率呢?MPLLCON(FCLK和Fin的比例關系)和CLKDIVN寄存器(FCLK、HCLK和PCLK之間的比例關系):FCLK=(2*m*Fin)/(p*2^s)

m=MDIV+8,p=PDIV+2,s=SDIV。(MPLLCON寄存器中)。注意:在系統初始化階段應該先初始化UPLL(USB時鐘),然后等待大約7個nop指令之后,再初始化MPLL.這也就是啟動代碼時,需要注意的。同時最好按照官方給出的系統時鐘配置參考。

例子:已知系統外部晶振輸入為12MHz,要求FCLK輸出為200MHz,經過計算可以得到MDIV=92,PDIV=4,SDIV=1。

M_MDIV EQU 92 //Fin=12.0MHz,Fout=200MHz

M_PDIV EQU 4

M_SDIV EQU 1

ldr r0 ,=MPLLCON

ldr r1 ,=((M_MDIV<<12)+(M_PDIV<<4)+M_SDIV)

str r1,[r0]

下面配置CLKDIVN寄存器,實現FCLK、HCLK、PCLK之間的分頻比。其中HDIVN用于控制FCLK和PCLK的比例關系;PDIVN主要用于控制HCLK和PCLK的比例關系。

定時器原理與應用

S3C2440有5個16位定時器,定時器0、1、2、3被稱為PWM定時器。定時器 4 是一個無輸出引腳的內部定時器。定時器 0 還包含用于大電流驅動的死區發生器。(時鐘源是PCLK)

定時器原理相同,寄存器TCMPBn和TCNTBn用于緩存定時器n的比較值和初始化值;TCON用于控制定時親的開啟與關閉;可以通過讀取寄存器TCNTOn得到定時器的當前計數值。

TCMPBn的值是用于脈寬調制(PWM)。當遞減計數器的值與定時器控制邏輯中的比較寄存器的值相匹配時定時器控制邏輯改變輸出電平。因此,比較寄存器決定 PWM 輸出的開啟時間(或關閉時間)。

定時器工作原理概述:

首先、將定時器的比較值和初始值裝入寄存器TCMPBn和TCNTBn中。

然后、設置定時器控制器TCON啟動定時器。此時、TCMPBn和TCNTBn中的值會加載到寄存器TCMPn和TCNRn中。

此時、定時器會減1計數,即TCNTn進行減1計數,當TCMPn=TCNTn時,TOUTn引腳輸出取反。TCNTn繼續減1計數。

當TCNTn的值到達0時,其輸出管腳TOUTn再次發轉,并觸發定時器n的中斷。(如果中斷使能的話)

當TCNTn的值到達0時,如果在TCON寄存器中將定時器n設置為“自動取反”,則自動加載初值,下一輪計數流程開始。

可以通過讀取TCNTOn讀取觀察定時器當前的值。PCLK經過兩級分頻器,輸出頻率作為定時器的工作頻率。

定時器配置寄存器TCFG0用于控制第1級分頻器的分頻系數,分頻器輸出頻率為:

PCLK/(prescaler value+1),其中prescaler value=0~255.

定時器配置寄存器TCFG1用于控制多路開關。

定時器的輸入時鐘=PCLK/(prescaler value+1)/(divider value)

prescaler value=0~255;divider value=2、4、8、16

例子:設置適當的分頻系數,使定時器0的輸入時鐘為62.5kHz

假如PCLK為50MHz,則50MHz/62.5kHz=800,可以是第一級分頻系數為100,第2級的分頻系數為8即可滿足要求。

rTCFG0 &= ~(0xFF);

rTCFG0 |=99;

rTCFG1 &=~(0xf);

rTCFG1 |=0x02;

總體思路是先將這幾位清零,然后將數據寫入這幾位。

WATCHDOG定時器可以像16位定時器一樣用于產生周期性的中斷,也可以用于發出復位信號以重啟失常的系統。

評論